# Free Electronic Lab

(formerly Fedora Electronic Lab)

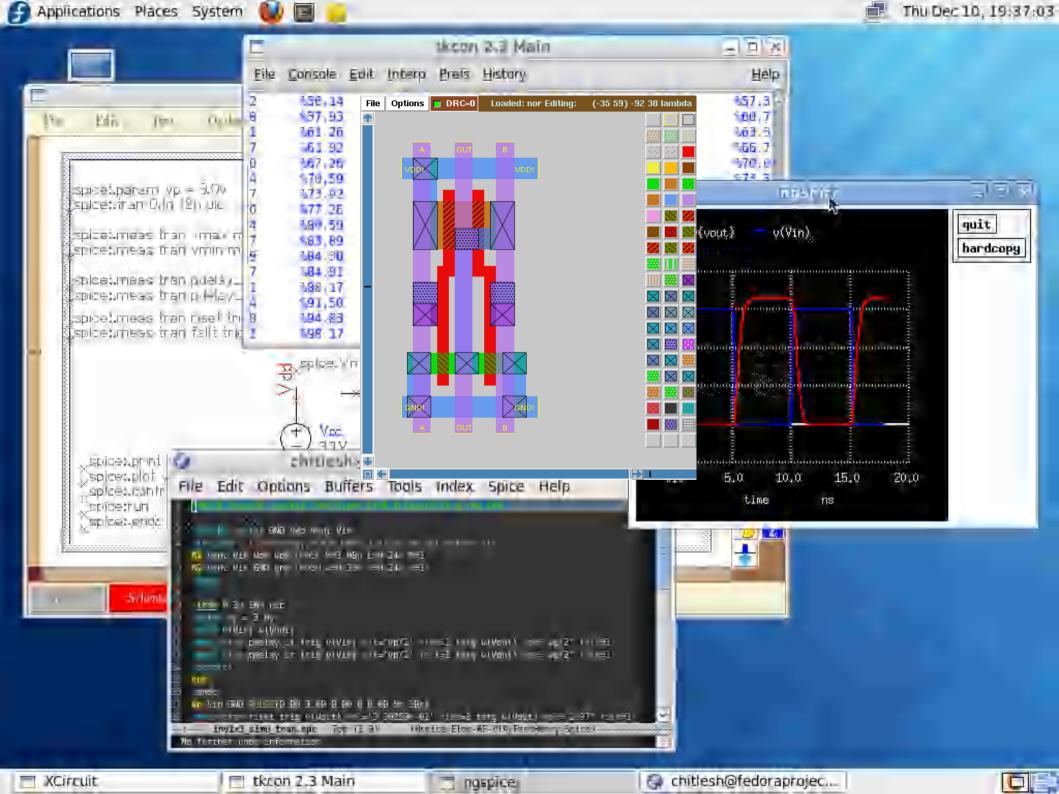

An opensource Design and Simulation platform for Micro-Electronics

A one-stop linux distribution for hardware design

**Marketing means for opensource EDA developers (Networking)**

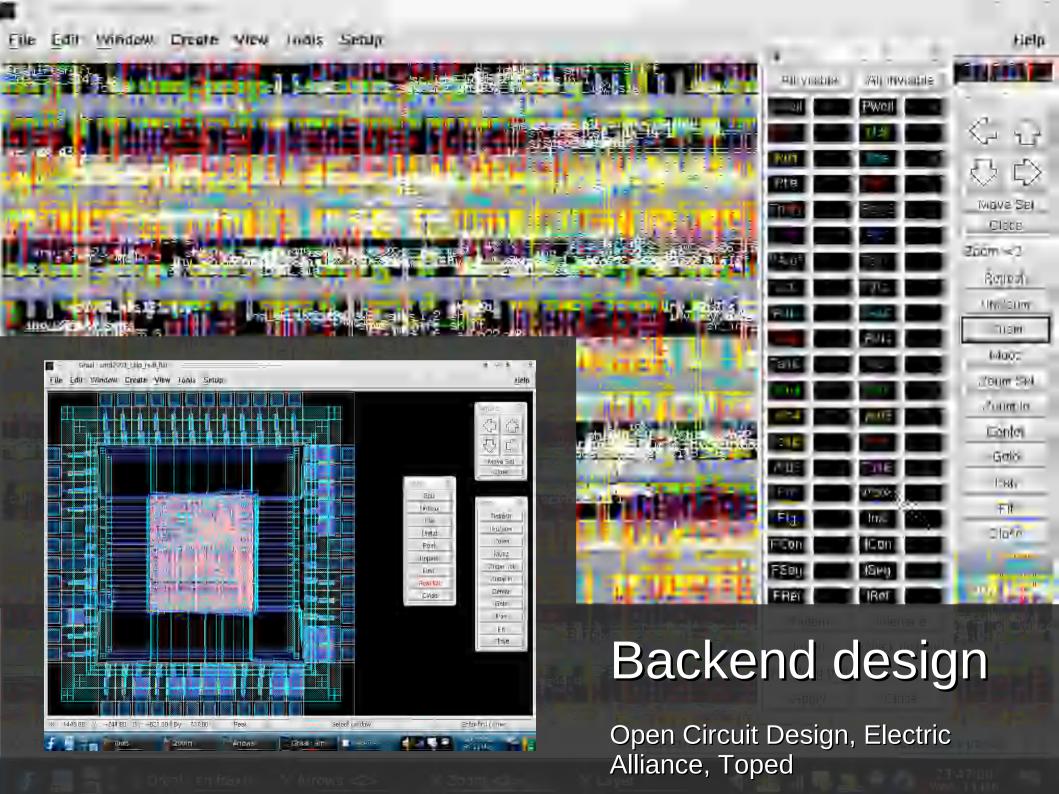

From SPEC, Model, Frontend Design, Backend, Development boards to embedded software.

### **Electronic Designers Problems**

Approx. 6 month design development cycle

**Tackling Design Complexity**

Lower Power, Lower Cost and Smaller Space

Semiconductor Industry's neck squeezed in 2008

Management (digital/analog) IP Portfolio

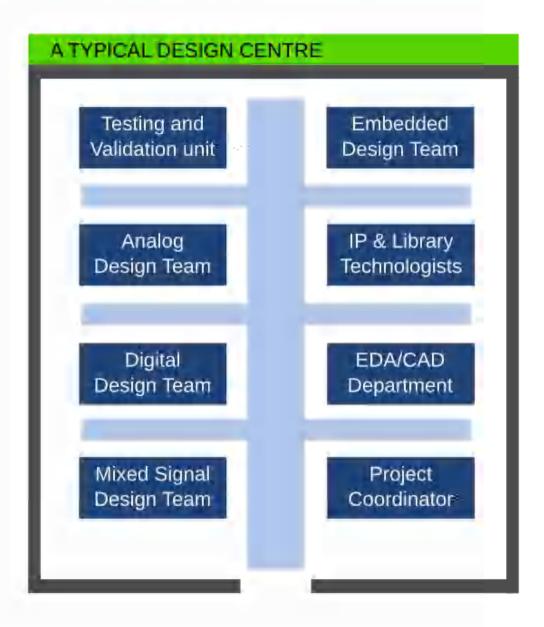

#### OVERVIEW: FEL'S SOLUTIONS TO THE DESIGN CENTER

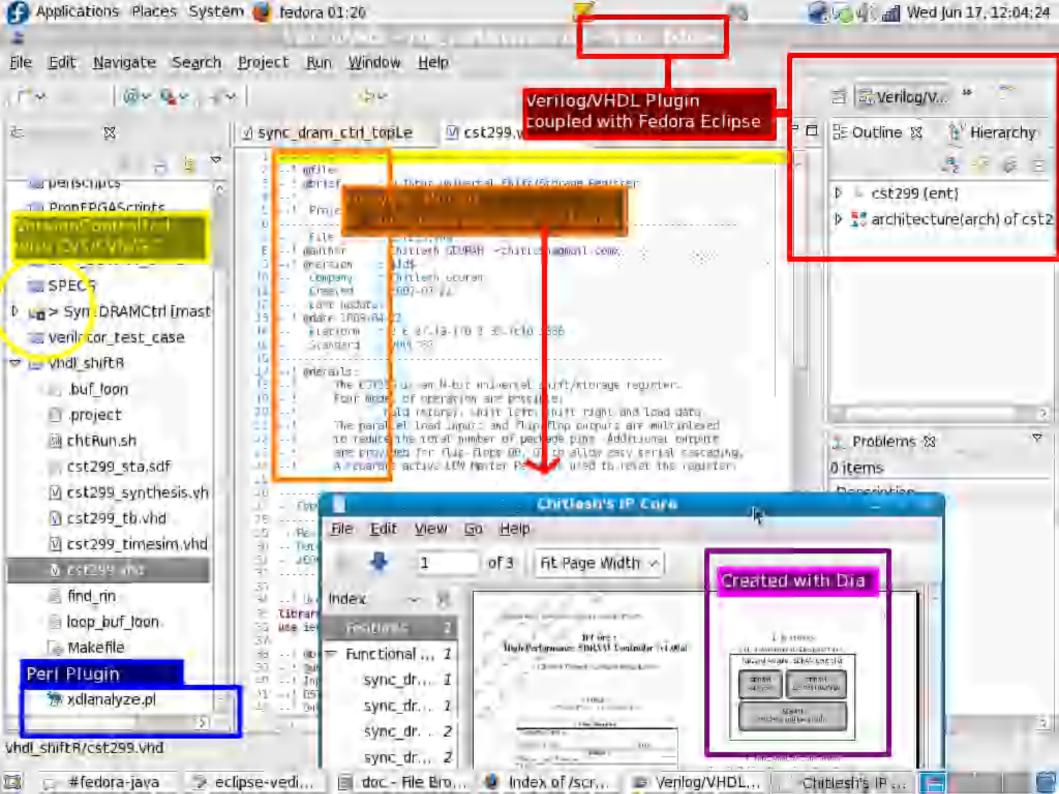

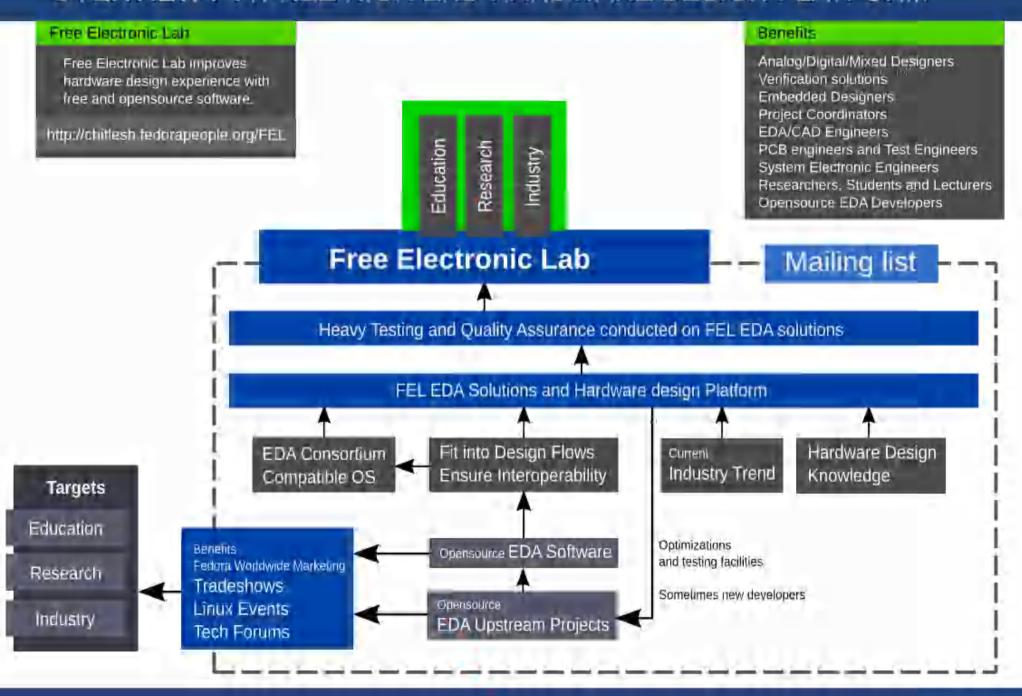

Providing EDA solutions for the real world requires a clear overview on the targetted users. Free Electronic Lab strives to fulfill all the needs of each stage of the design flow. Research Education Industry **FEL's Applications** Free Electronic Lab Free Electronic Lab improves hardware design experience with opensource software.

http://chitlesh.fedorapeople.org/FEL

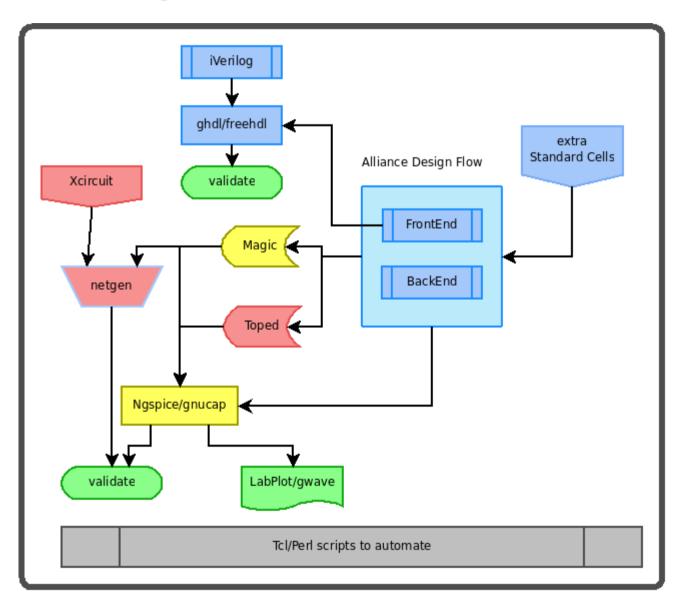

### A basic Design Flow

TIP: Use verilator to lint your verilog files.

Most of the Veripool tools are available under FEL. They are in sync with Wilson Snyder's releases.

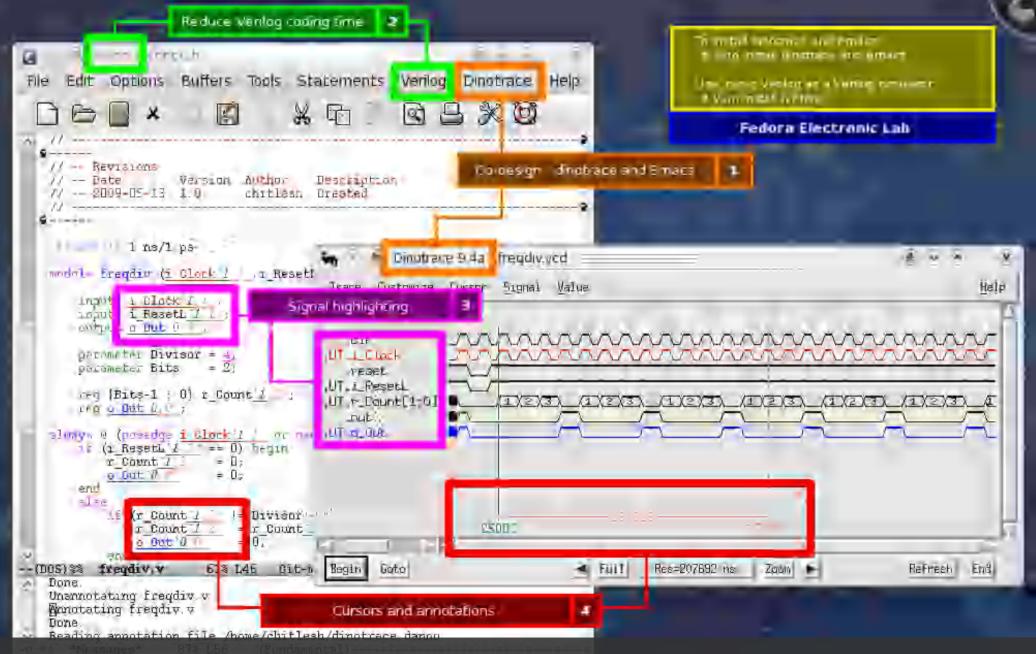

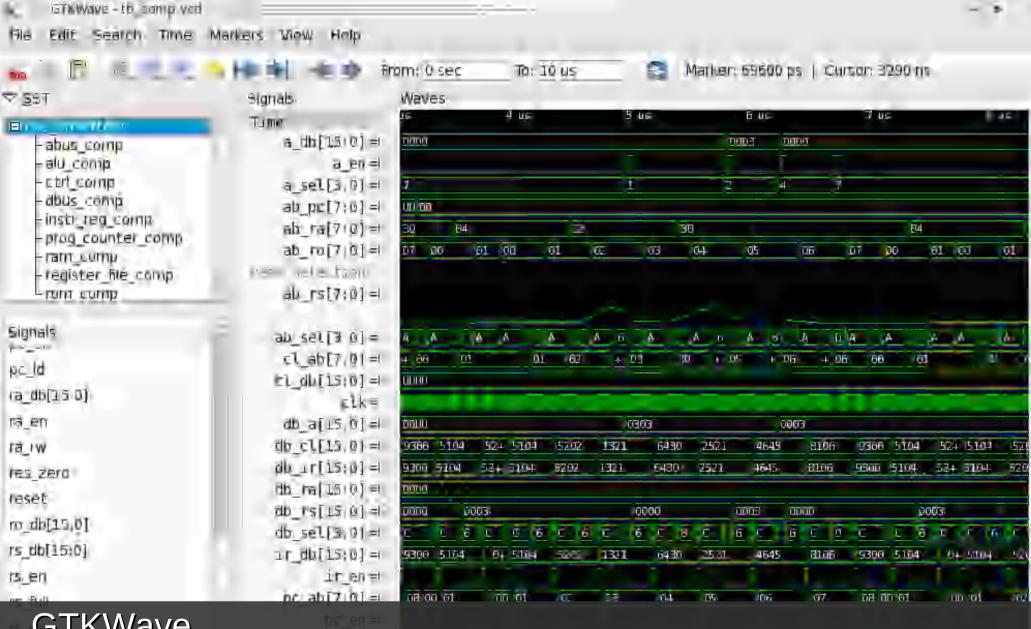

**GTKWave**

Don't forget its TCL backend Widely used together with SystemC

#### **Tools**

### **Standard Cell libraries**

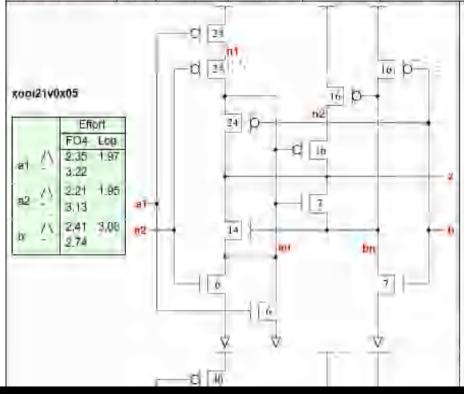

#### xooi21 standard cell family

2-I/P exclusive NOR gate with 2-OR input

NEXT

PREV

3 XNOR gates with OR gate input designed for minimum transistor count and hence smallest size. The OR gate is made by changing the inverter on the a input of a 2-XNOR gate into a 2-NOR gate. The Prop and Ramp delays below are the average of the inverting and non-inverting delays. The Syndosys Liberty formal. LIB file has the correct delays for each case.

| z:((a1+á2)^b)'<br>vsclib013 | t≅ll wiath |        |        | DOWEL    |         | Generic 0.13im typical timing (ps 8 ps/rF), nin s2. |        |       |       |       |

|-----------------------------|------------|--------|--------|----------|---------|-----------------------------------------------------|--------|-------|-------|-------|

|                             |            |        |        | leakayge | dynamic | IR=ProoR=RampR=Load(iF), IF=ProoF=RampF=Load(IF)    |        |       |       |       |

|                             | gales      | lambda | 0.13um | υM       | nWMHz   | FinCap                                              | PropR. | RampR | ProgF | RampF |

| xuai21v0x05                 | 3.0        | 72     | 3,96   | 0.67     | 19.7    | 3,71                                                | 104    | 6/34  | 105   | 4.76  |

| x00/21V0x1                  | 4.0        | 96     | 5,28   | 1.52     | 29,6    | 5.0f                                                | 94     | 3,7€  | 94    | 2,52  |

| xuoi21v0x2                  | 6.7        | 160    | 8,80   | 2.73     | 56.8    | 11.2f                                               | 32     | 1,96  | 39    | 1,27  |

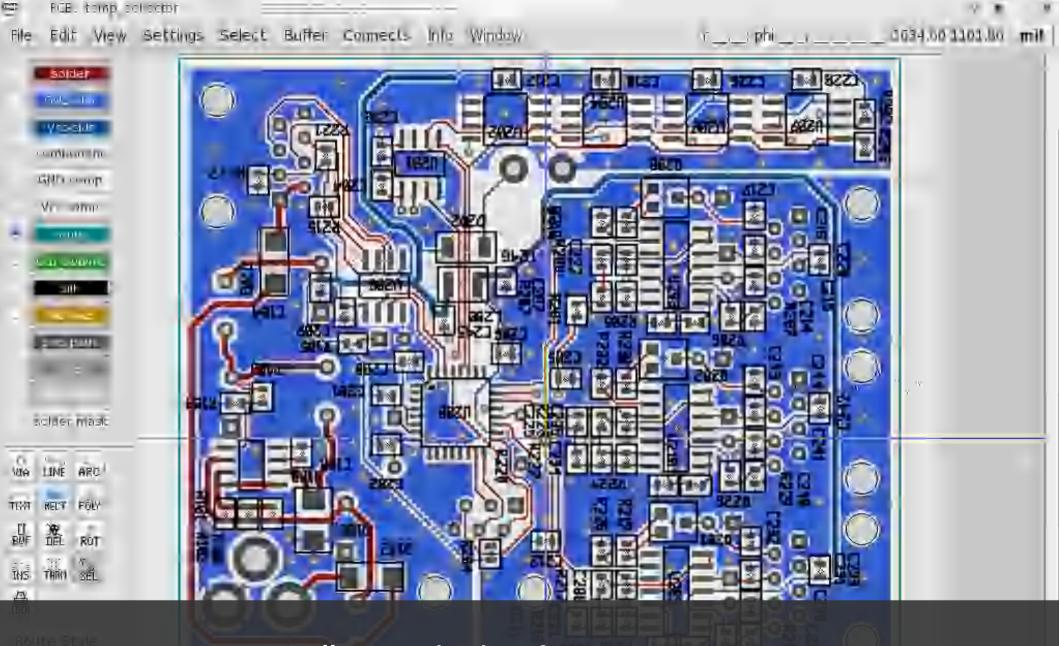

A Temperature Collector design from Levente Kovacs.

Active development and a 3D PCB layout design in development.

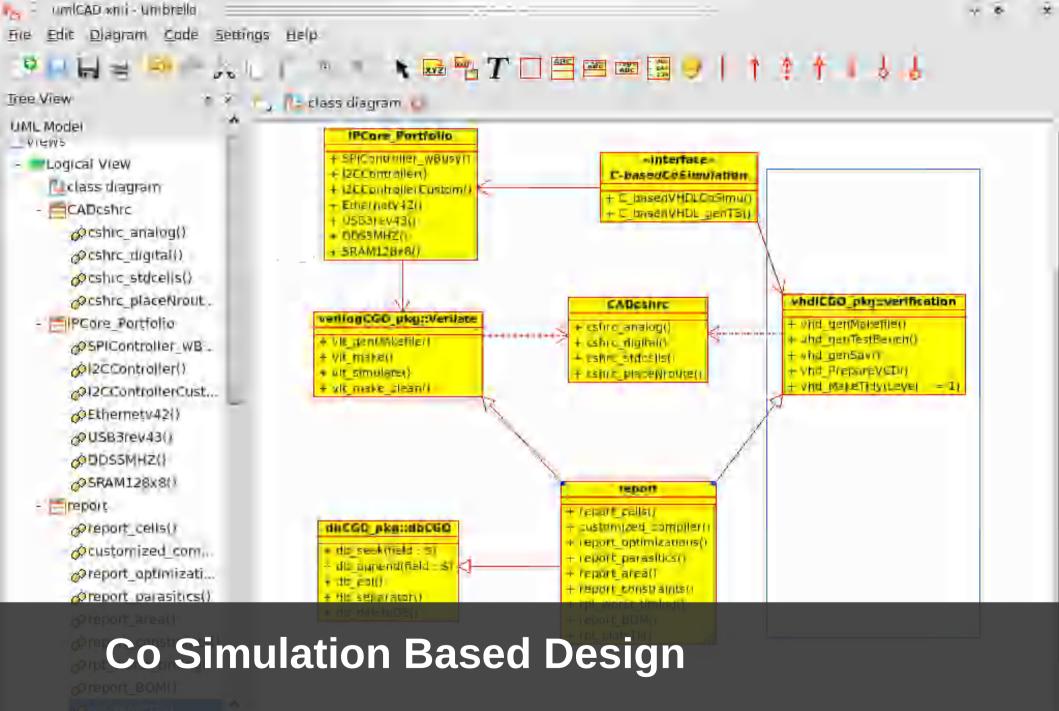

UML to Perl, TCL or C++ exports.

TIP: Heaven, when coupled with Truss & Teal tools.

#### OVERVIEW: A FREE HIGH END HARDWARE DESIGN PLATFORM

### **Simple Installation**

#### **Trial:**

Fedora Electronic Lab LiveDVD

#### **Production Environment:**

On Fedora > 12 or upcoming RHEL / CentOS 6

# yum groupinstall 'Electronic Lab'

### Who are using FEL?

Universities around the world

- US, UK, France, India, Mexico, Brazil, Italy

Small companies & consulting companies

Linux For You magazine Published twice (Jan 08, Jan 09)

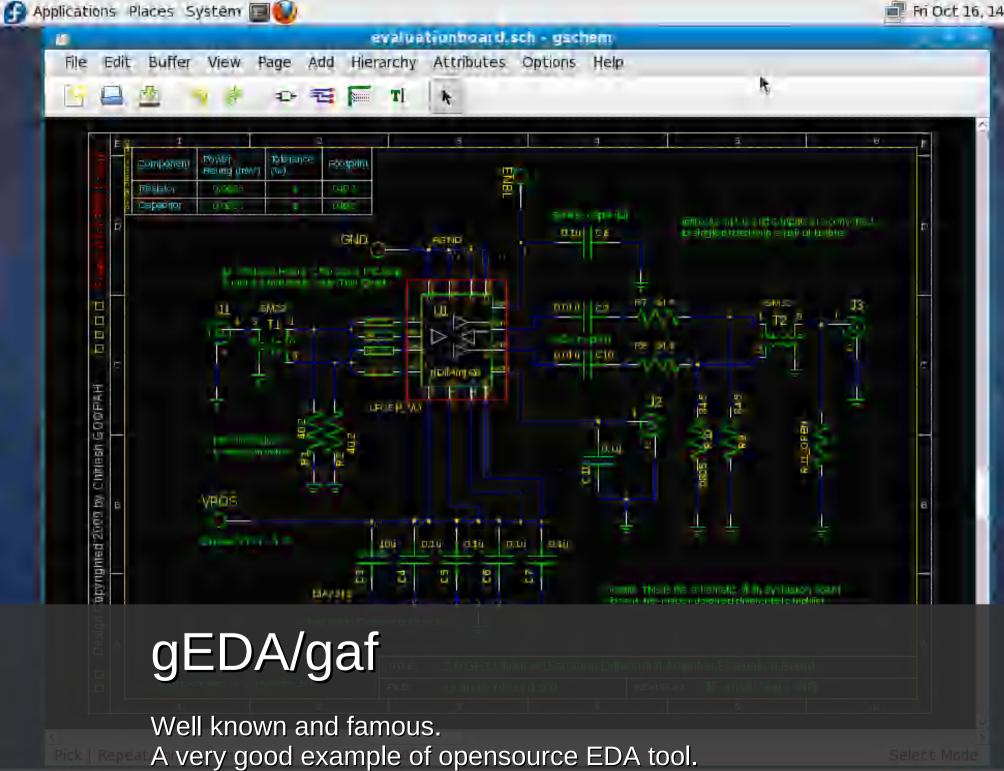

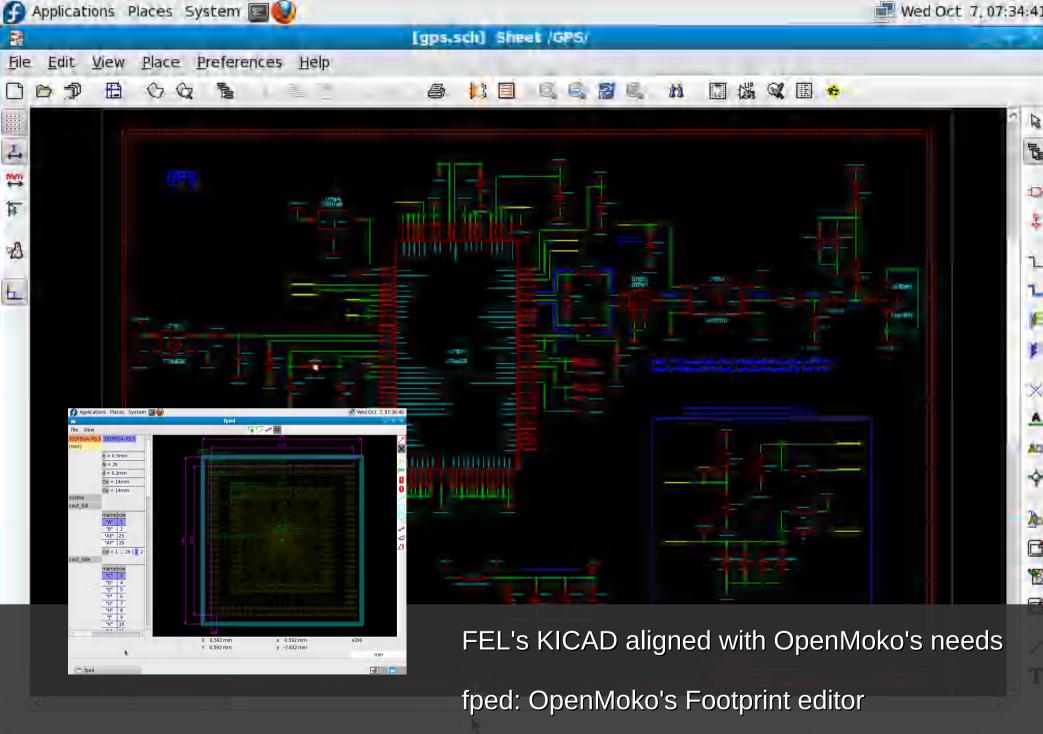

Basic opensource EDA tools

Sun Microsystems, IBM, ST Microelectronics,

Analog Devices, On Semi conductors

## **FEL User and Developer benefits**