### MOS MEMORY INTERFACE

- Dual Inverting MOS Driver

- Low Standby Power Dissipation

- Versatile Interface Circuit for Use between TTL Levels and Level-Shifted High-Current, High-Voltage Systems

- Inputs May Be Level-Shifted by Use of a Current Source or Capacitive Coupling or Driven Directly by a Voltage Source

- Designed to Be Functionally Interchangeable with National DS0026

## description

The SN75369 is a monolithic dual MOS driver and interface circuit that operates with either current-source or voltage-source input signals. The device accepts appropriate level-shifted input signals from TTL or other logic systems and provides high-current and high-voltage output levels suitable for driving MOS circuits. Specifically, it may be used to drive address, control, and/or timing inputs for several types of MOS RAMs and MOS shift registers.

The SN75369 operates from standard MOS and/or bipolar supplies in most applications. This device has been optimized for operation with VCC supply voltage from 12 volts to 20 volts positive with respect to VEE. However, it is designed so as to be usable over a wide range of VCC.

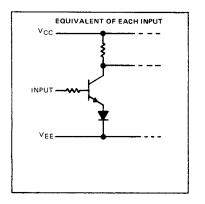

Inputs of the SN75369 are referenced to the VEE terminal and contain a series current-limiting resistor. The device will operate with either positive current input signals or voltage input signals that are positive with respect to VEE. In many applications the VEE terminal is connected to the MOS VDD supply of -12 volts to -15 volts with the inputs to be driven from TTL levels or other positive voltage levels. The required negative-level shifting may be done with an external p-n-p transistor current source or by use of capacitive coupling and appropriate input voltage pulse characteristics.

The SN75369 is characterized for operation from  $0^{\circ}$ C to  $70^{\circ}$ C.

- Capable of Driving High-Capacitance Loads

- Compatible with Many Popular MOS RAMs and MOS Shift Registers

- VCC Supply Voltage Variable over Wide Range to 22 Volts Maximum with Respect to VFF

- Operates from Standard Bipolar and/or MOS Supply Voltage

- High-Speed Switching

- Transient Overdrive Minimizes Power Dissipation

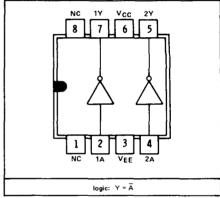

JG OR P

DUAL-IN-LINE PACKAGE (TOP VIEW)

NC - No internal connection

# TYPE SN75369 DUAL MOS DRIVER

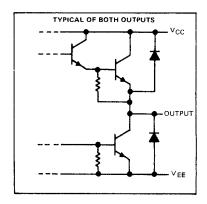

#### schematics of inputs and outputs

## absolute maximum ratings over operating free-air temperature range (unless otherwise noted)

| Supply voltage range of VCC (see Note 1)                                 | 0.5 V to 22 V |

|--------------------------------------------------------------------------|---------------|

| Input voltage                                                            |               |

| Continuous total dissipation at (or below) 25°C free-air temperature (se | ee Note 2):   |

| JG package                                                               | 825 mW        |

| P package                                                                |               |

| Operating free-air temperature range                                     | 0°C to 70°C   |

| Storage temperature range                                                |               |

|                                                                          | 300°C         |

| Lead temperature 1/16 inch from case for 10 seconds: P package           |               |

NOTES: 1. Voltage values are with respect to the  $V_{\mbox{\footnotesize{EE}}}$  terminal unless otherwise noted.

For operation above 25°C free-air temperature, refer to Dissipation Derating Curves in the Thermal Information section, which starts on page 21. In the JG package, SN75369 chips are glass-mounted.

## recommended operating conditions

|                                    | MIN  | NOM | MAX | UNIT |

|------------------------------------|------|-----|-----|------|

| Supply voltage, VCC                | 4.75 | 20  | 22  | V    |

| Operating free-air temperature, TA | 0    |     | 70  | °C   |

## definition of input logic levels

| PARAMETER                                | MIN TYP | MAX | UNIT |

|------------------------------------------|---------|-----|------|

| V <sub>IH</sub> High-level input voltage | 2.5     | 4.5 | V    |

| VIL Low-level input voltage              |         | 0.5 | V    |

| I <sub>IH</sub> High-level input current | 8       | 20  | mA   |

| I <sub>IL</sub> Low-level input current  |         | 27  | mA   |

## electrical characteristics over recommended ranges of VCC and operating free-air temperature (unless otherwise noted)

| PARAMETER       |                                       | TEST CONDITIONS (See Note 3)              |                                                 | MIN                  | TYP <sup>†</sup>     | MAX                  | UNIT   |

|-----------------|---------------------------------------|-------------------------------------------|-------------------------------------------------|----------------------|----------------------|----------------------|--------|

| VIK             | Input clamp voltage                   | I <sub>1</sub> =15 mA                     |                                                 |                      |                      | -1.5                 | V      |

|                 |                                       | V <sub>IL</sub> = 0.5 V,                  | I <sub>OH</sub> = -50 μA                        | V 1                  | V 07                 |                      |        |

| v <sub>OH</sub> | High-level output voltage             | I <sub>IL</sub> = 0.7 mA,                 | I <sub>OH</sub> = −50 μA                        | 7 VCC-1              | V <sub>CC</sub> -0.7 |                      | V      |

|                 |                                       | V <sub>IL</sub> ≈ 0.5 V,                  | 1 <sub>OH</sub> = -10 mA                        | V <sub>CC</sub> -2.3 | \/ 19                |                      | \ \ \  |

|                 |                                       | I <sub>IL</sub> = 0.7 mA,                 | l <sub>OH</sub> ≈ -10 mA                        |                      | ACC-170              |                      |        |

| VOL L           | Low-level output voltage              | V <sub>IH</sub> = 2.5 V,                  | I <sub>OL</sub> = 10 mA                         |                      | 0,15                 | 0.3                  |        |

|                 |                                       | I <sub>IH</sub> = 8 mA,                   | I <sub>OL</sub> = 10 mA                         |                      | 0.15                 | 0.3                  | V      |

|                 |                                       | $V_{CC} = 10 \text{ V to } 22 \text{ V},$ | VIH = 2.5 V, IOL = 30 mA                        | -                    | 0.2                  | 0.4                  |        |

|                 |                                       | V <sub>CC</sub> ≈ 10 V to 22 V,           | I <sub>IH</sub> ≈ 8 mA, I <sub>OL</sub> ≈ 30 mA |                      |                      |                      |        |

| Vok             | Output clamp voltage                  | V <sub>I</sub> = 0 V,                     | I <sub>OH</sub> = 20 mA                         |                      |                      | V <sub>CC</sub> +1.5 | ٧      |

|                 | Input voltage                         | I <sub>1</sub> = 20 mA                    |                                                 |                      | 3.7                  | 5                    |        |

| V <sub>I</sub>  |                                       | I <sub>1</sub> = 8 mA                     |                                                 | T                    | 2.4                  | 3                    | V      |

|                 |                                       | I <sub>1</sub> = 0.7 mA                   |                                                 |                      | 0.4                  | 0.6                  |        |

|                 | Input current                         | V <sub>1</sub> = 4,5 V                    |                                                 |                      | 27                   | 45                   |        |

| l <sub>1</sub>  |                                       | V <sub>I</sub> = 2.5 V                    |                                                 |                      | 9                    | 15                   | mA     |

|                 |                                       | V <sub>1</sub> = 0.5 V                    |                                                 |                      |                      | 1.5                  | 1      |

| 1               | Supply current from V <sub>CC</sub> , | V <sub>CC</sub> = 22 V,                   |                                                 |                      |                      | 0.5                  | mA     |

| (CC(H)          | both outputs high                     | Both inputs at 0 V,                       | No load                                         |                      |                      | 0.5                  | III.A  |

|                 | Supply current from V <sub>CC</sub> , | V <sub>CC</sub> = 22 V,                   |                                                 |                      | 7                    | 12                   | mA     |

| (CC(L)          | both outputs low                      | Both inputs at 3 V,                       | No load                                         |                      | ,                    | 12                   | I IIIA |

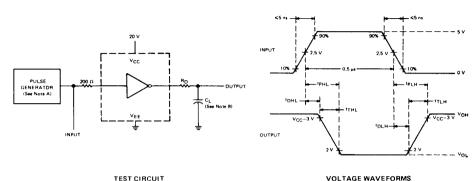

## switching characteristics, VCC = 20 V, TA = 25°C

| PARAMETER        |                                                  | TEST CONDITIONS                                    | MIN | TYP | MAX | UNIT |

|------------------|--------------------------------------------------|----------------------------------------------------|-----|-----|-----|------|

| †DLH             | Delay time, low-to-high level output             |                                                    | 8   | 16  | 24  | ns   |

| †DHL             | Delay time, high-to-low-level output             | 0                                                  | 4   | 11  | 20  | ns   |

| †TLH             | Transition time, low-to-high-level output        | C <sub>L</sub> ≃ 390 pF,<br>R <sub>D</sub> = 10 Ω, | 8   | 18  | 30  | ns   |

| <sup>t</sup> THL | Transition time, high-to-low-level output        | See Figure 1                                       | 6   | 16  | 30  | ns   |

| <sup>t</sup> PLH | Propagation delay time, low-to-high-level output | See Figure ?                                       | 16  | 35  | 54  | ns   |

| <sup>†</sup> PHL | Propagation delay time, high-to-low-level output |                                                    | 10  | 28  | 50  | ns   |

<sup>†</sup>All typical values are at  $V_{CC} = 20 \text{ V}$  and  $T_A = 25^{\circ}\text{C}$ .

NOTE 3: Many of these parameters are specified independently for either voltage source or current source external forcing functions at the inputs. Use the appropriate set of specifications for each application.

#### PARAMETER MEASUREMENT INFORMATION

NOTES: A. The pulse generator has the following characteristics: PRR = 1 MHz,  $Z_{out} \approx 50~\Omega_{\odot}$

B. C<sub>L</sub> includes probe and jig capacitance.

#### FIGURE 1-SWITCHING TIMES, EACH DRIVER

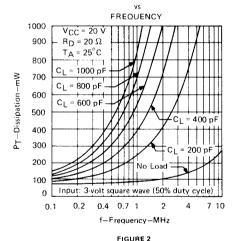

## TYPICAL CHARACTERISTICS

TDTAL DISSIPATION (BDTH DRIVERS)

## TYPICAL APPLICATION DATA

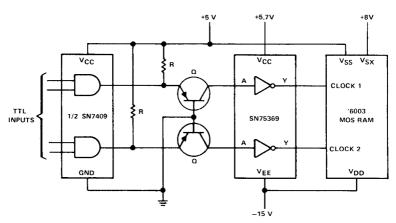

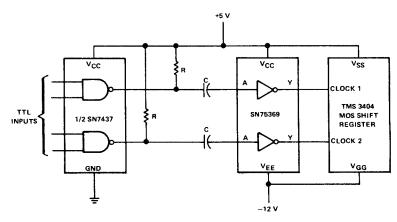

Applications of the SN75369 used as an interface device in systems converting TTL signals to negative-polarity MOS clock signals are shown in Figures 3 and 4. In both applications the SN75369 VEE pin is connected to a negative MOS supply voltage. Figure 3 and 4 show the use of the SN75369 over a wide range of VCC supply voltages. The device may even be used as a TTL level driver, if desired, by connecting VCC to 5 volts.

Both applications shown require negative level shifting from positive voltage levels to the inputs of the SN75369, which are referenced to the VEE terminal. A p-n-p transistor current source is used to level shift in Figure 3. Resistor R sets the current and an open-collector TTL gate is used to switch the p-n-p transistor. Figure 4 shows capacitive coupling being used to level shift. The SN7437 TTL buffer gate is used as a voltage source driver with pull-up resistor R providing additional high-level drive. The value of coupling capacitor C depends on the frequency and characteristics of the signal applied to the capacitor.

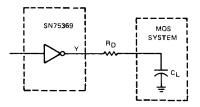

The fast switching speeds of the SN75369 may produce undersirable output transient overshoot because of load or wiring inductance. A small series damping resistor may be used to reduce or eliminate this output transient overshoot. The optimum value of the damping resistor depends on the specific load characteristics and switching speed. A typical value would be between  $10~\Omega$  and  $30~\Omega$ . See Figure 5.

NOTES: A. R  $\approx$  350  $\Omega$  to 500  $\Omega$ . B. Q is 2N3829 or equivalent.

FIGURE 3-MOS RAM CLOCK DRIVER SYSTEM WITH P-N-P TRANSISTOR CURRENT SOURCE USED TO SHIFT LEVELS TO INPUTS OF \$N75369

## TYPICAL APPLICATION DATA

NOTE A: R  $\approx$  100  $\Omega$  to 250  $\Omega$ .

FIGURE 4-MOS SHIFT REGISTER CLOCK ORIVER SYSTEM WITH CAPACITIVE COUPLING USEO

TO SHIFT LEVELS TO INPUTS OF SN75369

NOTE:  $R_D \approx 10~\Omega$  to 30  $\Omega$  (optional)

FIGURE 5--USE OF DAMPING RESISTOR TO REDUCE OR ELIMINATE OUTPUT TRANSIENT OVERSHOOT IN CERTAIN SN75369 APPLICATIONS