# BC2161 Sub-1GHz OOK Transmitter with Encoder

#### **Features**

- Operating voltage: V<sub>DD</sub>=2.2V~3.6V

- Complete Sub-1GHz OOK (BT=0.5) modulation transmitter

- · Key input function

- 2 key inputs for the 8-pin SOP-EP package type

- 8 key inputs for the 16-pin NSOP-EP package types

- Avoid battery exhaust due to jammed button (MAX FCNT[7:0])

- Frequency bands: 315MHz, 433MHz, 868MHz, 915MHz

- Integrated 320-bit FUSE data memory

- Output power of up to 13dBm

- Supports 2-wire I<sup>2</sup>C interface

- Low sleep current of 0.4μA

- TX current consumption @ 433MHz:

- TYP. 18.5mA(10dBm, Data=1)/Typ. 11.2mA (10dBm, 50% duty cycle)

- Programmable symbol rate from 1.5ksps to 24ksps for OOK modulation

- Integrated full range VCO, loop filter and Fractional-N PLL synthesizer

- · Supports 16MHz crystal

- 4-step programmable TX Power: 0/5/10/13 dBm

- FCC / ETSI Compliant

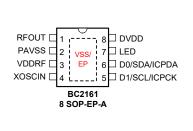

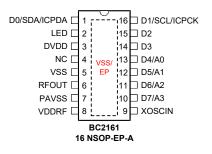

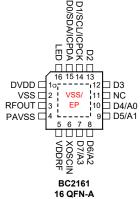

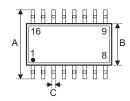

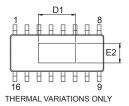

- Small size package types: 8-pin SOP-EP, 16-pin NSOP-EP/QFN

#### **Abbreviation Notes**

- TX: RF Transmitter

- SX: Synthesizer

- PA: Power Amplifier

- OOK: On-Off Keying

- PLL: Phase Lock Loop

- MMD: Multi-Mode Divider

- XTAL: External Crystal

### **Development Tools**

For rapid product development and to simplify device parameter setting, Holtek has provided relevant development tools which users can download from the following link:

https://www.holtek.com/rf-chip-parameters-setting-tool

### **General Description**

The BC2161 is a highly integrated OOK transmitter for remote wireless applications. The transmitter is a true "data-in, antenna-out" monolithic device making it very easy for users to implement wireless systems.

The BC2161 can operate at the 315MHz, 433MHz, 868MHz and 915MHz frequency bands. It supports an OOK modulation scheme and can operate with a symbol rate of up to 24ksps.

The BC2161 offers a programmable output power level. It is capable of delivering +13dBm maximum power into a  $50\Omega$  load. The BC2161 adopts agile state machines to ease the control and minimize the power consumption. With an external crystal and a few external components, the BC2161 can implement a complete solution for an effective RF transmitter.

These features can be easily programmed through  $I^2C$  interface or internal FUSE. With these combined features the BC2161 can provide a power-saving and cost effective solution for a huge range of remote wireless applications.

Rev. 1.81 1 October 29, 2021

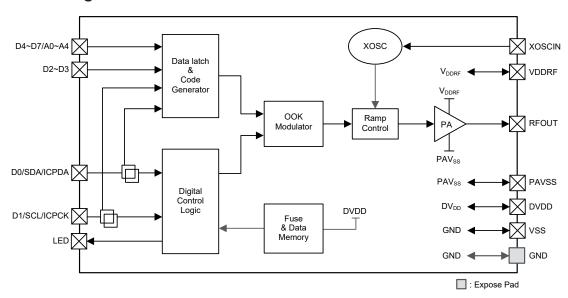

### **Block Diagram**

# **Pin Assignment**

# **Pin Description**

The function of each pin is listed in the following table. Note that where more than one package type exists the table will reflect the situation for the 16-pin NSOP-EP package type.

| Pin No. | Pin Name     | Function      | Type | Description                                                          |

|---------|--------------|---------------|------|----------------------------------------------------------------------|

|         |              | D0            | I    | Data input                                                           |

| 1       | D0/SDA/ICPDA | SDA           | I/O  | I <sup>2</sup> C data pin                                            |

|         |              | ICPDA         | I/O  | ICP data pin                                                         |

| 2       | LED          | LED           | 0    | LED indicator                                                        |

| 3       | DVDD         | DVDD          | PWR  | RF digital positive power supply                                     |

| 4       | NC           | No connection | _    | _                                                                    |

| 5       | VSS          | Ground        | PWR  | Ground                                                               |

| 6       | RFOUT        | PA_OUT        | AO   | RF output signal from power amplifier  – Connect to matching circuit |

| 7       | PAVSS        | VSSRF_PA      | PWR  | RF ground                                                            |

| 8       | VDDRF        | VDDRF         | PWR  | Analog positive power supply                                         |

| 9       | XOSCIN       | Crystal       | Al   | Crystal input                                                        |

| 10~13   | D4/A0~D7/A3  | D4/A0~D7/A3   | I    | Compound pin Data / Address / Key Trigger input                      |

| 14,15   | D2, D3       | D2, D3        | I    | Data input                                                           |

|         |              | D1            | I    | Data input                                                           |

| 16      | D1/SCL/ICPCK | SCL           | I    | I <sup>2</sup> C clock pin                                           |

|         |              | ICPCK         | I    | ICP clock pin                                                        |

| _       | VSS/EP       | Ground        | PWR  | Exposed pad, must be connected to ground                             |

Legend: I: Digital Input O: Digital Output AI: Analog Input

AO: Analog Output PWR: Power

# **Absolute Maximum Ratings**

| Supply Voltage        | $V_{SS}$ -0.3V to $V_{SS}$ +3.6V |

|-----------------------|----------------------------------|

| Voltage on I/O Pins   | $V_{SS}$ -0.3V to $V_{DD}$ +0.3V |

| Storage Temperature   | -55°C to 150°C                   |

| Operating Temperature | -40°C to 85°C                    |

| ESD HBM               | ±2kV                             |

<sup>\*</sup> Devices being ESD sensitive. HBM (Human Body Mode) is based on MIL-STD-883.

Note: These are stress ratings only. Stresses exceeding the range specified under "Absolute Maximum Ratings" may cause substantial damage to the device. Functional operation of this device at other conditions beyond those has listed in the specification is not implied and prolonged exposure to extreme conditions may affect device reliability.

Rev. 1.81 3 October 29, 2021

## D.C. Characteristics

$\label{eq:table_power} Ta=25^{\circ}\text{C, V}_{\text{DD}}=3.3\text{V, f}_{\text{XTAL}}=16\text{MHz, OOK modulation with Matching circuit,} \\ PAOUT is powered by V_{\text{DD}}=3.3\text{V, unless otherwise noted.}$

| Symbol               | Parameter                                  | Description                               | Min.               | Тур. | Max.            | Unit |  |

|----------------------|--------------------------------------------|-------------------------------------------|--------------------|------|-----------------|------|--|

| V <sub>DD</sub>      | Operating Voltage                          | _                                         | 2.2                | 3.3  | 3.6             | V    |  |

| T <sub>A</sub>       | Operating Temperature                      | _                                         | -40                | _    | 85              | °C   |  |

| T <sub>FP</sub>      | FUSE Program Temperature                   | _                                         | _                  | 25   | _               | °C   |  |

| V <sub>IH</sub>      | High Level Input Voltage                   | _                                         | 0.7V <sub>DD</sub> | _    | V <sub>DD</sub> | V    |  |

| V <sub>IL</sub>      | Low Level Input Voltage                    | _                                         | 0                  | _    | $0.3V_{DD}$     | V    |  |

| V <sub>OH</sub>      | High Level Output Voltage                  | @I <sub>OH</sub> =-5mA                    | 0.8V <sub>DD</sub> | _    | V <sub>DD</sub> | V    |  |

| V <sub>OL</sub>      | Low Level Output Voltage                   | @I <sub>oL</sub> =5mA                     | 0                  | _    | $0.2V_{DD}$     | V    |  |

| Current Consumptions |                                            | I <sub>Sleep</sub> in the Deep Sleep Mode | _                  | 0.4  | _               | μΑ   |  |

|                      |                                            | I <sub>L</sub> Data low & PA off current  | _                  | 6.0  | _               | mA   |  |

|                      | 0 40 5 0 0 0 0 1                           | P <sub>OUT</sub> =0dBm                    | _                  | 10.5 | _               |      |  |

|                      | (Data=1)                                   | P <sub>OUT</sub> =10dBm                   | _                  | 18.5 | _               | mA   |  |

|                      |                                            | P <sub>OUT=</sub> 13dBm                   | _                  | 24.5 | _               |      |  |

|                      | Current Consumption @ 433MHz Band (Data=1) | P <sub>OUT=</sub> 0dBm                    | _                  | 11.0 | _               |      |  |

|                      |                                            | P <sub>OUT=</sub> 10dBm                   | _                  | 18.5 | _               | mA   |  |

|                      | (Data-1)                                   | P <sub>OUT=</sub> 13dBm                   | _                  | 25.0 | _               |      |  |

| I <sub>H</sub>       |                                            | P <sub>OUT</sub> =0dBm                    | _                  | 13.5 | _               |      |  |

|                      | (Data-1)                                   | P <sub>OUT=</sub> 10dBm                   | _                  | 20.0 | _               | mA   |  |

|                      |                                            | P <sub>OUT</sub> =13dBm                   | _                  | 24.5 | _               |      |  |

|                      |                                            | P <sub>OUT=</sub> 0dBm                    | _                  | 12.5 | _               |      |  |

|                      | Current Consumption @ 915MHz Band (Data=1) | P <sub>OUT=</sub> 10dBm                   | _                  | 19   | _               | mA   |  |

|                      | (Data-1)                                   | P <sub>OUT=</sub> 13dBm                   | _                  | 24   | _               |      |  |

### A.C. Characteristics

### **RF Characteristics**

$\label{eq:tau} Ta=25^{\circ}\text{C}, \ V_{\text{DD}}=3.3\text{V}, \ f_{\text{XTAL}}=16\text{MHz}, \ \text{OOK modulation with Matching circuit}, \\ \text{PAOUT is powered by } V_{\text{DD}}=3.3\text{V}, \ \text{unless otherwise noted}.$

| Symbol               | Parameter                         | Condition                 | Min.       | Тур. | Max.       | Unit  |

|----------------------|-----------------------------------|---------------------------|------------|------|------------|-------|

| ZRF                  |                                   |                           |            |      |            |       |

|                      |                                   |                           |            | 315  |            |       |

| f.                   | RF Operating Frequency Range      |                           |            | 433  |            | MHz   |

| f <sub>RF</sub>      | RF Operating Frequency Range      | _                         | _          | 868  | _          | IVITZ |

|                      |                                   |                           |            | 915  |            |       |

| XTAL                 |                                   |                           |            |      |            |       |

| f <sub>XTAL</sub>    | RF Operating XTAL Frequency       | General case              | _          | 16   | _          | MHz   |

| ESR                  | XTAL Equivalent Series Resistance | _                         | -          | _    | 100        | Ω     |

| CL                   | XTAL Capacitor Load               | _                         | _          | 16   | _          | pF    |

|                      | XTAL Tolerance <sup>(1)</sup>     | _                         | _          | ±20  | _          | ppm   |

| t <sub>Startup</sub> | XTAL Startup Time <sup>(2)</sup>  | _                         | _          | 1    | _          | ms    |

| PLL                  |                                   |                           |            |      |            |       |

| f <sub>STEP</sub>    | RF Frequency Synthesizer Step     | _                         | _          | 0.5  | _          | kHz   |

|                      | DLL Dhasa Naisa @ 422MLT          | Phase Noise @ 100k offset |            | -78  |            |       |

| DN                   | PLL Phase Noise @ 433MHz          | Phase Noise @ 1M offset   | ] <u> </u> | -105 | 1 <b>–</b> | dBc/  |

| PN <sub>PLL</sub>    | DLL Dhoop point @ 969MHz          | Phase Noise @ 100k offset |            | -68  |            | Hz    |

|                      | PLL Phase noise @ 868MHz          | Phase Noise @ 1M offset   |            | -100 |            |       |

Rev. 1.81 4 October 29, 2021

| Symbol            | Parameter                                               | Condition                                                                               | Min. | Тур. | Max. | Unit |

|-------------------|---------------------------------------------------------|-----------------------------------------------------------------------------------------|------|------|------|------|

| TX                |                                                         |                                                                                         |      |      |      |      |

|                   | Symbol Rate                                             | OOK modulation                                                                          | 1.5  | _    | 24   | ksps |

| _                 | DE Transmitter Output Dawer                             | @ 433MHz                                                                                | 0    | _    | 13   | dBm  |

| P <sub>OUT</sub>  | RF Transmitter Output Power                             | @ 868MHz                                                                                | 0    | _    | 13   | чын  |

| ER <sub>OOK</sub> | OOK Extinction Ratio                                    | OOK Modulation depth                                                                    | _    | 70   | _    | dB   |

|                   |                                                         | @ 315MHz                                                                                |      | 400  |      |      |

|                   | Occupied Bandwidth                                      | @ 433MHz                                                                                |      |      |      | kHz  |

|                   | (OOK, -20dBc)                                           | @ 868MHz                                                                                |      |      | -    |      |

|                   |                                                         | @ 915MHz                                                                                |      |      |      |      |

|                   |                                                         | f < 1GHz                                                                                | _    | _    | -36  |      |

| SE <sub>TX</sub>  | Transmitter Spurious Emission (P <sub>OUT</sub> =10dBm) | 47MHz < f < 74MHz<br>87.5MHz < f < 118MHz<br>174MHz < f < 230MHz<br>470MHz < f < 790MHz | _    | _    | -54  | dBm  |

|                   |                                                         | 2 <sup>nd</sup> , 3 <sup>rd</sup> Harmonic                                              | _    | _    | -30  |      |

Note: 1. This is the total tolerance including (1)Initial tolerance (2)Crystal loading (3)Aging and (4)Temperature dependence.

2. Depend on crystal property.

### I<sup>2</sup>C Characteristics

Ta=-40°C~85°C, Ta=25°C Typical

| Symbol                 | Parameter                                      | Test Conditions | Min. | Тур. | Max. | Unit |  |  |

|------------------------|------------------------------------------------|-----------------|------|------|------|------|--|--|

| I <sup>2</sup> C Chara | C Characteristics                              |                 |      |      |      |      |  |  |

| f <sub>SCL</sub>       | Serial Clock Frequency                         | _               | _    | _    | 1    | MHz  |  |  |

| t <sub>BUF</sub>       | Bus Free Time between Stop and Start Condition | SCL=1MHz        | 250  | _    | _    | ns   |  |  |

| t <sub>LOW</sub>       | SCL Low Time                                   | SCL=1MHz        | 500  | _    | _    | ns   |  |  |

| t <sub>HIGH</sub>      | SCL High Time                                  | SCL=1MHz        | 500  | _    | _    | ns   |  |  |

| t <sub>su(DAT)</sub>   | Data Setup Time                                | SCL=1MHz        | 100  | _    | _    | ns   |  |  |

| t <sub>su(STA)</sub>   | Start Condition Setup Time                     | SCL=1MHz        | 250  | _    | _    | ns   |  |  |

| t <sub>su(STO)</sub>   | Stop Condition Setup Time                      | SCL=1MHz        | 250  | _    | _    | ns   |  |  |

| t <sub>h(DAT)</sub>    | Data Hold Time                                 | SCL=1MHz        | 100  | _    | _    | ns   |  |  |

| t <sub>h(STA)</sub>    | Start Condition Hold Time                      | SCL=1MHz        | 250  | _    | _    | ns   |  |  |

| t <sub>r(SCL)</sub>    | Rise Time of SCL Signal                        | SCL=1MHz        | _    | _    | 100  | ns   |  |  |

| t <sub>f(SCL)</sub>    | Fall Time of SCL Signal                        | SCL=1MHz        | _    | _    | 100  | ns   |  |  |

| t <sub>r(SDA)</sub>    | Rise Time of SDA Signal                        | SCL=1MHz        | _    | _    | 100  | ns   |  |  |

| t <sub>f(SDA)</sub>    | Fall Time of SDA Signal                        | SCL=1MHz        | _    | _    | 100  | ns   |  |  |

Rev. 1.81 5 October 29, 2021

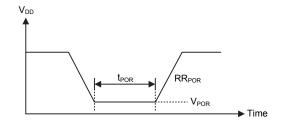

#### **Power on Reset Electrical Characteristics**

-40°C to 85°C Ta=25°C Typical

| Symbol            | nbol Parameter                                         |                        | Test Conditions |       | Тур. | Max.   | Unit  |

|-------------------|--------------------------------------------------------|------------------------|-----------------|-------|------|--------|-------|

| Symbol            | Farameter                                              | <b>V</b> <sub>DD</sub> | Conditions      | Min.  | iyp. | IVIAX. | Ullit |

| V <sub>POR</sub>  | V <sub>DD</sub> Start Voltage to Ensure Power-on Reset | _                      | _               |       | _    | 100    | mV    |

| RR <sub>POR</sub> | V <sub>DD</sub> Rising Rate to Ensure Power-on Reset   | _                      | _               | 0.035 | _    | _      | V/ms  |

| t <sub>POR</sub>  |                                                        | _                      | _               | 1     | _    | _      | ms    |

### **Functional Description**

This fully integrated RF transmitter can operate in the 315MHz, 433MHz, 868MHz and 915MHz frequency bands. The additional of a crystal and a limited number of external components are all that is required to create a complete and versatile RF transmitter system. The device includes an internal power amplifier and is capable of delivering up to +13dBm. Such a power level enables a small form factor transmitter to operate near the maximum transmission regulation limits. The device can operate with OOK receiver type.

To provide extra user flexibility, the device contains an area of FUSE memory, which is a kind of one-time programmable non-volatile memory. If the FUSE has not been programmed, which can be determined by checking the EFPGM bit in the CFG0 register, users should connect the device to an MCU and setup the relevant RF register configurations in the I<sup>2</sup>C Mode using an I<sup>2</sup>C interface. For devices whose FUSE are already programmed, the FUSE memory contents will be copied to the relevant registers automatically. However, the registers will be reset to their initial state when the device is powered off.

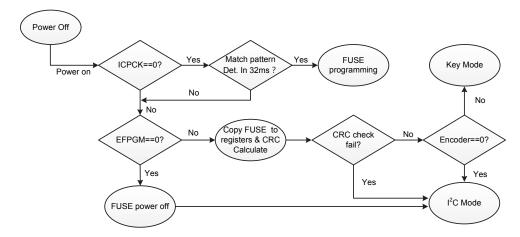

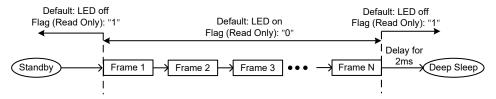

#### **State Control**

The device has integrated state machines that control the state transition between the different modes.

#### **Power-on States**

Rev. 1.81 6 October 29, 2021

After power on, if the ICPCK pin is kept at a High level by the internal pull-high function and the EFPGM bit state is high, the FUSE data will be automatically copied to the corresponding registers and will be also used for CRC calculation. If the EFPGM bit state is low, the FUSE power will be turned off and the device will enter the I<sup>2</sup>C mode.

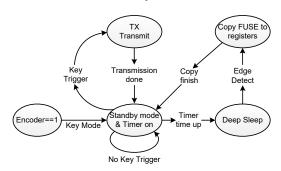

#### **Key Mode**

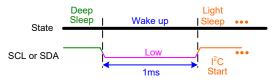

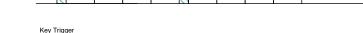

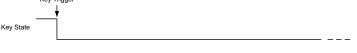

If users want to enter the Key mode, the Fuse must be programmed, the Encoder bit should be set high. During the Standby mode, if there is no key trigger event, the device will enter the Deep Sleep Mode after a 2ms delay. When a key trigger event occurs, which is a level trigger generated by pressing a button for more than 1ms, the transmitter will start to transfer data. The interval between data frames can be figured out using the following equation: 2ms × (FRAME GAP[2:0]). The transmission will end when the Frame counter stops. The device will then enter the Deep Sleep Mode after a fixed delay time of 2ms. In the Deep Sleep Mode, the clock stops and register configurations will all be reset. The device can only be woken up by an edge detection, which is implemented by pulling the Key pins from high to low. After this happens the FUSE memory will be automatically copied to the relevant registers and the device will enter the Standby mode.

#### **FUSE ICP Mode**

After powering on, the device checks the ICPCK pin state, which is active low but which will be pulled high by the internal pull high function. By adding this procedure, the device can still enter the programming interface to check the programmed value even if it has been programmed. For the 8-pin package applications, it is recommended that the D0 pin should be used as a Key. As the device clock frequency is 16MHz, the device will enter the ICP Mode for FUSE programming after a delay time of 32ms. Note that the FUSE can only be programmed once.

Rev. 1.81 7 October 29, 2021

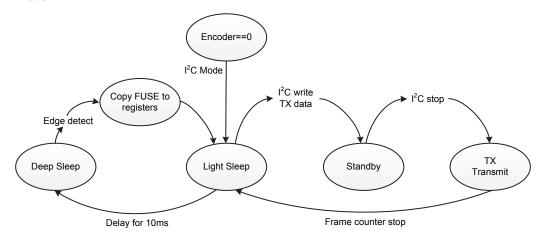

#### I<sup>2</sup>C Mode

The device will enter the I<sup>2</sup>C Mode if the Encoder bit is low. Note that in the I<sup>2</sup>C mode, the device should be connected with an MCU and operate as an I<sup>2</sup>C slave. During the Light Sleep Mode, the timer will be on and will start counting. After a delay time of 10ms the device will enter the Deep Sleep Mode. If a toggle action occurs on the SDA or SCL pin, the timer will be reset and will restart counting. The device can be woken up from the Deep Sleep Mode if a falling edge is detected on pin SCL or SDA. Here it should be noted that the high-to-low pulse should be maintained for at least 1ms. In this situation the FUSE data will be copied to the registers again and the device will return to the Light Sleep Mode. In this way the MCU can generate a complete I<sup>2</sup>C format to initiate the follow-up state machine. To start a data transmission, the I<sup>2</sup>C write TX data procedure must be executed first and when finished the TX transmission will be initiated after the I<sup>2</sup>C stop. The frames are transmitted continuously, the TX transmission ends when the frame counter stops after which the device will return to the Light Sleep Mode.

Note: In the Key Mode, pins D0~D7 can be used as key triggers, however in the I<sup>2</sup>C Mode, pins D0~D7 have no key trigger function and only pins D0 and D1 have wake-up functions. Therefore it is suggested that for the 16-pin package types, pins D2~D7 should be pulled high in the I<sup>2</sup>C Mode.

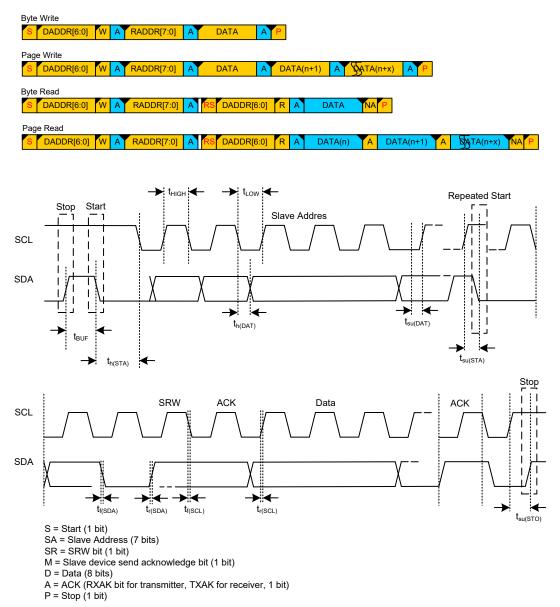

### I<sup>2</sup>C Serial Programming

In the I<sup>2</sup>C Mode, the MCU can configure the internal relevant registers using I<sup>2</sup>C serial programming. The transmitter only supports the I<sup>2</sup>C format for byte write, page write, byte read and page read formats. The transmission procedure is shown below.

It should be noted that the I<sup>2</sup>C is a non-standard I<sup>2</sup>C interface, which only supports a single device for connection.

- · Symbol definition

- · S: Start symbol

- RS: Repeat Start

- P: Stop symbol

- DADDR[6:0]: device address, 21h

- R/W: read write select, R(0):write, (1): read

- RADDR[7:0]: register address

- ACK: A(0): ACK, NA(1): NAK

- · Bus Direction:

- Host to device:

Device to host:

I<sup>2</sup>C Communication Timing Diagram

#### **Programming Methodology**

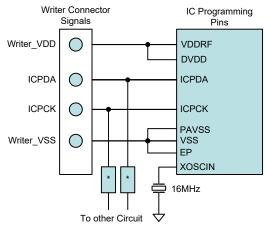

The device programming interface should utilise an adaptor with an integrated 16MHz crystal.

| Programming Function | Pin Name                  | Pin Description  |

|----------------------|---------------------------|------------------|

| ICPCK                | ICPCK                     | ICP clock        |

| ICPDA                | ICPDA                     | ICP data/address |

| VDD                  | VDDRF & DVDD              | Power supply     |

| VSS, EP              | PAVSS & VSS & Exposed-Pad | Ground           |

| XTAL IN<br>(Adaptor) | XOSCIN                    | IC system clock  |

When programming the device needs to be located on a Socket with a 16MHz crystal connected between pin XOSCIN and ground. Holtek provides an e-link or e-WriterPro tool for communication with the PC. Between the e-link and the device there are four interconnecting lines, namely VDD, VSS, ICPCK and ICPDA pins.

Note: \* may be resistor or capacitor - the resistance of \* must be greater than  $1k\Omega$  and the capacitance of \* must be less than 1nF.

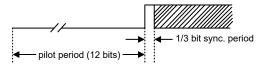

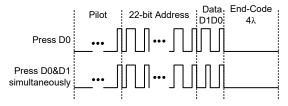

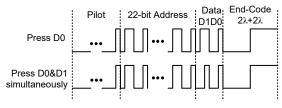

#### **Encoder Packet Example – OOK Modulation**

Packet Structure:

In the above structure, the procedures enclosed in brackets mean optional and can therefore be disabled. The rest are leading code, address and data, which are necessary parts of the packet. These parameters can be configured but can never be disabled.

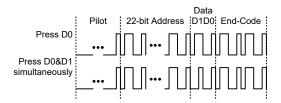

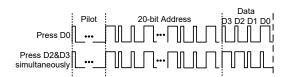

### Example 1: HT6P20B

#### Format:

| Pilot(24 λ) | Address(22-bit) | Data(2-bit) | End(4-bit) |

|-------------|-----------------|-------------|------------|

Pilot code is  $24\lambda \rightarrow LEAD\_CODE[2:0]=000b$ ;

Address: [155555h], Address Length is 22-bit  $\rightarrow$  ADDR\_LEN[2:0]=100b;

DATA: 2 Keys (D1/D0)  $\rightarrow$  KEY\_SEL[1:0]=00b;

End code is 4-bit  $\rightarrow$  END\_CODE[1:0]=01b;

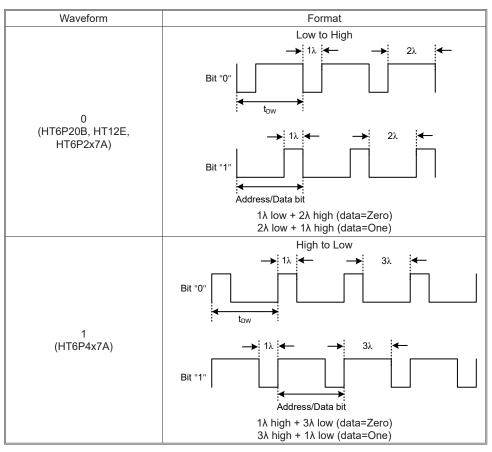

Bit format: Low to High → Waveform=0b;

$\rightarrow$  1 $\lambda$  low + 2 $\lambda$  high (Data=Zero) / 2 $\lambda$  low + 1 $\lambda$  high (Data=One)

#### Example 2: HT6P20D

#### Format:

| Pilot(24 λ) | Address(20-bit) | Data(4-bit) | End(4-bit) |

|-------------|-----------------|-------------|------------|

Pilot code is  $24\lambda \rightarrow LEAD\_CODE[2:0]=000b$ ;

Address: [55555h]; Address Length is 20-bit  $\rightarrow$  ADDR LEN[2:0]=011b;

DATA: 4 Keys  $(D3/D2/D1/D0) \rightarrow KEY SEL[1:0]=01b$ ;

End code is 4-bit  $\rightarrow$  END CODE[1:0]=01b;

Bit format: Low to High → Waveform=0b;

$\rightarrow$  1 $\lambda$  low + 2 $\lambda$  high (Data=Zero) / 2 $\lambda$  low + 1 $\lambda$  high (Data=One)

#### Example 3: HT6P427A

#### Format:

| Pilot(32 λ)   | Address(20-bit)  | Data(4-bit) |

|---------------|------------------|-------------|

| 1 1101(02 11) | 71001000(20 211) | Bata(1 bit) |

Pilot code is  $32\lambda \rightarrow LEAD\_CODE[2:0]=001b$ ;

Address: [99999h]; Address Length is 20-bit  $\rightarrow$  ADDR LEN[2:0]=011b;

DATA: 4 Keys  $(D3/D2/D1/D0) \rightarrow KEY SEL[1:0]=01b$ ;

Bit format: High to Low  $\rightarrow$  Waveform=1b;

$\rightarrow$  1 $\lambda$  high + 3 $\lambda$  low (Data=Zero) / 3 $\lambda$  high + 1 $\lambda$  low (Data=One)

#### Example 4: HT6P437A

#### Format:

| Pilot(32 λ) Address(20-bit) Address(4-bit) Data(4-bit) | Pilot(32 λ) | Internal<br>Address(20-bit) | External<br>Address(4-bit) | Data(4-bit) |

|--------------------------------------------------------|-------------|-----------------------------|----------------------------|-------------|

|--------------------------------------------------------|-------------|-----------------------------|----------------------------|-------------|

Pilot code is  $32\lambda \rightarrow \text{LEAD CODE}[2:0]=001b$ ;

Address: [DDDDDh] + Dipswitch; Address Length is 20-bit  $\rightarrow$  ADDR LEN[2:0]=011b;

DATA: 4 Dipswitches (A3/A2/A1/A0) + 4 Keys (D3/D2/D1/D0) → KEY\_SEL[1:0]=10b;

Bit format: High to Low  $\rightarrow$  Waveform=1b;

$\rightarrow$  1 $\lambda$  high + 3 $\lambda$  low (Data=Zero) / 3 $\lambda$  high + 1 $\lambda$  low (Data=One)

#### Example 5: HT6P237A

#### Format:

| Pilot(24 λ) | Address(22-bit) | Data(2-bit) | End(4-bit) |

|-------------|-----------------|-------------|------------|

Pilot code is  $24\lambda \rightarrow LEAD\_CODE[2:0]=000b$ ;

Address: [3EEEEEh]; Address Length is 22-bit  $\rightarrow$  ADDR LEN[2:0]=100b;

DATA: 2 Keys (D1/D0)  $\rightarrow$  KEY\_SEL[1:0]=00b;

End code is 4-bit  $\rightarrow$  END CODE[1:0]=01b;

Bit format: Low to High  $\rightarrow$  Waveform=0b;

$\rightarrow$  1 $\lambda$  low + 2 $\lambda$  high (Data=Zero) / 2 $\lambda$  low + 1 $\lambda$  high (Data=One)

#### Example 6: HT6P247A

### Format:

| Pilot(24 λ)  | Address(24-bit)  | Data(4-bit) | Fnd(4-bit)  |

|--------------|------------------|-------------|-------------|

| 1 1101(2+11) | /tdd1c55(Z+ bit) | Data(+ bit) | Lild(+ bit) |

Pilot code is  $24\lambda \rightarrow LEAD\_CODE[2:0]=000b$ ;

Address: [777777h]; Address Length is 24-bit  $\rightarrow$  ADDR\_LEN[2:0]=101b;

DATA: 4 Keys  $(D3/D2/D1/D0) \rightarrow KEY\_SEL[1:0]=01b$ ;

End code is 4-bit  $\rightarrow$  END CODE[1:0]=01b;

Bit format: Low to High  $\rightarrow$  Waveform=0b;

$\rightarrow$  1 $\lambda$  low + 2 $\lambda$  high (Data=Zero) / 2 $\lambda$  low + 1 $\lambda$  high (Data=One)

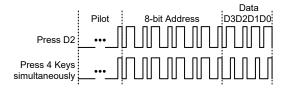

#### Example 7: HT12E

#### Format:

| Pilot(37 λ) | Address(8-bit) | Data(4-bit) |

|-------------|----------------|-------------|

|             |                |             |

Pilot code is  $37\lambda \rightarrow LEAD\_CODE[2:0]=010b$ ;

Address: [55h]; Address Length is 8-bit  $\rightarrow$  ADDR\_LEN[2:0]=000b;

DATA: 4 Keys  $(D3/D2/D1/D0) \rightarrow KEY\_SEL[1:0]=01b$ ;

Bit format: Low to High  $\rightarrow$  Waveform=0b;

$\rightarrow$  1 $\lambda$  low + 2 $\lambda$  high (Data=Zero) / 2 $\lambda$  low + 1 $\lambda$  high (Data=One)

#### **Example 8: Custom Format**

#### Format:

| Pilot  | Start | Address | Data    | CRC     | End   |

|--------|-------|---------|---------|---------|-------|

| (16 λ) | (6 λ) | (8-bit) | (4-bit) | (8-bit) | (4 λ) |

Pilot code is  $16\lambda \rightarrow \text{LEAD CODE}[2:0]=100b$ ;

Start code is  $6\lambda \rightarrow START_BIT[1:0]=01b$ ;

Address: [93h]; Address Length is 8-bit  $\rightarrow$  ADDR\_ LEN[2:0]=000b;

DATA: 4 Keys  $(D3/D2/D1/D0) \rightarrow KEY\_SEL[1:0]=01b$ ;

CRC: 8-bit  $\rightarrow$  CRC[1:0]=10b;

End Code is  $4\lambda \rightarrow \text{END CODE}[1:0]=10b$ ;

Bit format: High to Low  $\rightarrow$  Waveform=1b;

$\rightarrow$  1 $\lambda$  high + 3 $\lambda$  low (Data=Zero) / 3 $\lambda$  high + 1 $\lambda$  low (Data=One)

### **Fuse Register Map**

This list provides a summary of all internal registers. Their detailed operation is described under their relevant section in the functional description.

|         | Register | Bit      |                             |          |          |           |          |          |          |  |  |

|---------|----------|----------|-----------------------------|----------|----------|-----------|----------|----------|----------|--|--|

| Address | Name     | 7        | 6                           | 5        | 4        | 3         | 2        | 1        | 0        |  |  |

| 00h     | CFG0     | Reserved | Reserved EFPGM XO_TRIM[5:0] |          |          |           |          |          |          |  |  |

| 01h     | CFG1     | FR       | AME_GAP[2                   | 2:0]     |          |           | Reserved |          |          |  |  |

| 02h     | CFG2     |          | Reserved                    |          |          |           |          |          |          |  |  |

| 03h     | CFG3     |          |                             |          | Rese     | erved     |          |          |          |  |  |

| 04h     | CFG4     |          |                             |          | Rese     | erved     |          |          |          |  |  |

| 05h     | CFG5     |          |                             |          | Rese     | erved     |          |          |          |  |  |

| 06h     | CFG6     |          |                             |          | Rese     | erved     |          |          |          |  |  |

| 07h     | CFG7     |          |                             |          | Rese     | erved     |          |          |          |  |  |

| 08h     | CFG8     |          |                             |          | Rese     | erved     |          |          |          |  |  |

| 09h     | CFG9     |          |                             |          | Rese     | erved     |          |          |          |  |  |

| 0Ah     | CFG10    |          | D_K                         | [3:0]    |          |           | TXPV     | /R[3:0]  |          |  |  |

| 0Bh     | CFG11    |          |                             | D_       | N[5:0]   |           |          | BAND_    | SEL[1:0] |  |  |

| 0Ch     | CFG12    |          |                             |          | D_K[     | [11:4]    |          |          |          |  |  |

| 0Dh     | CFG13    |          |                             |          | D_K[′    | 19:12]    |          |          |          |  |  |

| 0Eh     | CFG14    |          | BI                          | T_WIDTH[ | 4:0]     |           |          | AD_CODE[ |          |  |  |

| 0Fh     | CFG15    | ΑI       | DDR_LEN[2                   | :0]      | START    | _BIT[1:0] | Waveform |          |          |  |  |

| 10h     | CFG16    | Reserved | Encoder                     | Res      | served   | CRC_S     | SEL[1:0] | KEY_S    | SEL[1:0] |  |  |

| 11h     | CFG17    |          |                             |          | Rese     | erved     |          | -        |          |  |  |

| 12h     | CFG18    |          |                             |          | Rese     | erved     |          |          |          |  |  |

| 13h     | CFG19    |          |                             |          | Rese     | erved     |          |          |          |  |  |

| 14h     | CFG20    |          |                             |          | Rese     | erved     |          | _        |          |  |  |

| 15h     | CFG21    |          |                             |          | ENCODER_ | ADDRL[7:0 | ]        |          |          |  |  |

| 16h     | CFG22    |          |                             |          | ENCODER_ | ADDRM[7:0 | )]       |          |          |  |  |

| 17h     | CFG23    |          |                             |          | ENCODER_ | ADDRH[7:0 | ]        |          |          |  |  |

| 18h     | CFG24    |          |                             |          | ENCODER_ | ADDRU[7:0 | ]        |          |          |  |  |

| 19h     | CFG25    |          |                             |          | FRAME_0  | CNTR[7:0] |          |          |          |  |  |

| 1Ah     | CFG26    |          |                             |          | Rese     | erved     |          |          |          |  |  |

| 1Bh     | CFG27    |          |                             |          | 1        | erved     |          |          |          |  |  |

| 1Ch     | CFG28    | Reserved | TXD_INV                     | TXD_REV  | LED_SWD  |           | Rese     | erved    |          |  |  |

| 1Dh     | CFG29    |          |                             |          |          | erved     |          |          |          |  |  |

| 1Eh     | CFG30    |          |                             |          |          | CNT[7:0]  |          |          |          |  |  |

| 1Fh     | CFG31    |          |                             |          |          | C_L[7:0]  |          |          |          |  |  |

| 20h     | CFG32    |          |                             |          | EFCRC    | _H[7:0]   |          |          |          |  |  |

| 21h     | CFG33    |          |                             |          | Reserved |           |          |          | TX_FLAG  |  |  |

| 22h     | CFG34    |          |                             |          |          | erved     |          |          |          |  |  |

| 23h     | CFG35    |          |                             |          | Rese     | erved     |          |          |          |  |  |

| 24h     | CFG36    |          |                             |          |          | erved     |          |          |          |  |  |

| 25h     | CFG37    |          |                             |          |          | erved     | -        |          |          |  |  |

| 26h     | CFG38    |          |                             |          |          | erved     |          |          |          |  |  |

| 27h     | CFG39    |          |                             |          |          | erved     |          |          |          |  |  |

| 28h     | CFG40    |          |                             |          | 1ºC_[    | DATA      |          |          |          |  |  |

If the Fuse is un-programmed, the BC2161 device will have a default state, determined by register initial values.

Operating Frequency: 433.92MHz TX Output Power: 10dBm

XTAL Capacitor Load: 14.85pF Encoding Format: HT6P427A

Symbol Rate: 4ksps Encoder: I<sup>2</sup>C Mode

### • CFG0: Configuration Control Register 0

| Address | Bit           | 7        | 6     | 5 | 4 | 3     | 2       | 1 | 0 |

|---------|---------------|----------|-------|---|---|-------|---------|---|---|

|         | Name          | Reserved | EFPGM |   |   | XO_TR | IM[5:0] |   |   |

| 00h     | R/W           | R/W      | R     |   |   | R/    | W       |   |   |

|         | Initial Value | 1        | 0     | 1 | 0 | 0     | 0       | 0 | 0 |

Bit 7 Reserved, must be [0b1]

Bit 6 **EFPGM**: FUSE programmed, read only by the Holtek RF Tool

0: Fuse is not programmed – FUSE data is not mapped to the configuration registers

1: Fuse is programmed – FUSE data is mapped to the configuration registers

Bit 5~0 XO\_TRIM[5:0]: Trim the internal capacitor load value for the crystal

| XO_TRIM[5:0] | Equiv. C <sub>∟</sub> (pF) |

|--------------|----------------------------|

| 0            | 9.87                       |

| 4            | 10.00                      |

| 8            | 10.12                      |

| 12           | 11.44                      |

| 16           | 12.16                      |

| 17           | 12.33                      |

| 18           | 12.49                      |

| 20           | 12.83                      |

| 24           | 13.50                      |

| 28           | 14.15                      |

| XO_TRIM[5:0] | Equiv. C <sub>L</sub> (pF) |

|--------------|----------------------------|

| 32           | 14.85                      |

| 36           | 15.48                      |

| 40           | 16.16                      |

| 44           | 16.81                      |

| 48           | 17.49                      |

| 52           | 18.07                      |

| 56           | 18.67                      |

| 60           | 19.20                      |

| 63           | 19.61                      |

|              |                            |

### • CFG1: Configuration Control Register 1

|   | Address | Bit           | 7   | 6        | 5     | 4        | 3 | 2   | 1 | 0 |

|---|---------|---------------|-----|----------|-------|----------|---|-----|---|---|

|   |         | Name          | FRA | AME_GAP[ | [2:0] | Reserved |   |     |   |   |

|   | 01h     | R/W           |     | R/W      |       |          |   | R/W |   |   |

| ı |         | Initial Value | 0   | 0        | 0     | 1        | 0 | 1   | 0 | 1 |

Bit 7~5 FRAME\_GAP[2:0]: TX frame interval time

$t = 2ms \times (FRAME\_GAP[2:0])$

000: 0ms 001: 2ms 010: 4ms 011: 6ms 100: 8ms 101: 10ms

110: 12ms 111: 14ms

Bit 4~0 Reserved, must be [0b10101]

### • CFG2: Configuration Control Register 2

| Address | Bit           | 7 | 6        | 5 | 4  | 3 | 2 | 1 | 0 |  |

|---------|---------------|---|----------|---|----|---|---|---|---|--|

|         | Name          |   | Reserved |   |    |   |   |   |   |  |

| 02h     | R/W           |   |          |   | R/ | W |   |   |   |  |

|         | Initial Value | 1 | 0        | 1 | 1  | 0 | 1 | 1 | 0 |  |

Bit 7~0 Reserved, must be [0b10110110]

### • CFG3: Configuration Control Register 3

| Address | Bit           | 7 | 6 | 5 | 4    | 3     | 2 | 1 | 0 |

|---------|---------------|---|---|---|------|-------|---|---|---|

|         | Name          |   |   |   | Rese | erved |   |   |   |

| 03h     | R/W           |   |   |   | R/   | W     |   |   |   |

|         | Initial Value | 0 | 1 | 0 | 0    | 0     | 0 | 0 | 1 |

Bit 7~0 Reserved, must be [0b01000001]

### • CFG4: Configuration Control Register 4

| Address | Bit           | 7        | 6 | 5 | 4  | 3 | 2 | 1 | 0 |

|---------|---------------|----------|---|---|----|---|---|---|---|

|         | Name          | Reserved |   |   |    |   |   |   |   |

| 04h     | R/W           |          |   |   | R/ | W |   |   |   |

|         | Initial Value | 0        | 1 | 0 | 0  | 0 | 0 | 1 | 0 |

Bit 7~0 Reserved, must be [0b01000010]

### • CFG5: Configuration Control Register 5

| Address | Bit           | 7 | 6 | 5 | 4 | 3 | 2 | 1 | 0 |

|---------|---------------|---|---|---|---|---|---|---|---|

|         | erved         |   |   |   |   |   |   |   |   |

| 05h     | R/W           |   |   |   |   |   |   |   |   |

|         | Initial Value | 0 | 0 | 0 | 1 | 0 | 1 | 0 | 0 |

Bit 7~0 Reserved, must be [0b00010100]

### • CFG6: Configuration Control Register 6

| Address | Bit           | 7 | 6 | 5 | 4    | 3     | 2 | 1 | 0 |

|---------|---------------|---|---|---|------|-------|---|---|---|

|         | Name          |   |   |   | Rese | erved |   |   |   |

| 06h     | R/W           |   |   |   | R/   | W     |   |   |   |

|         | Initial Value | 1 | 0 | 0 | 1    | 1     | 0 | 0 | 1 |

Bit 7~0 Reserved, must be [0b10011001]

### • CFG7: Configuration Control Register 7

| Address | Bit           | 7 | 6        | 5 | 4 | 3 | 2 | 1 | 0 |  |  |

|---------|---------------|---|----------|---|---|---|---|---|---|--|--|

|         | Name          |   | Reserved |   |   |   |   |   |   |  |  |

| 07h     | R/W           |   | R/W      |   |   |   |   |   |   |  |  |

|         | Initial Value | 0 | 1        | 0 | 1 | 1 | 0 | 0 | 0 |  |  |

Bit 7~0 Reserved, must be [0b01011000]

### • CFG8: Configuration Control Register 8

| Address | Bit           | 7        | 6 | 5 | 4 | 3 | 2 | 1 | 0 |  |

|---------|---------------|----------|---|---|---|---|---|---|---|--|

|         | Name          | Reserved |   |   |   |   |   |   |   |  |

| 08h     | R/W           | R/W      |   |   |   |   |   |   |   |  |

|         | Initial Value | 1        | 0 | 1 | 0 | 0 | 0 | 1 | 0 |  |

Bit 7~0 Reserved, must be [0b10100010]

Rev. 1.81 14 October 29, 2021

### • CFG9: Configuration Control Register 9

| Address | Bit           | 7 | 6        | 5 | 4 | 3 | 2 | 1 | 0 |  |  |

|---------|---------------|---|----------|---|---|---|---|---|---|--|--|

|         | Name          |   | Reserved |   |   |   |   |   |   |  |  |

| 09h     | R/W           |   | R/W      |   |   |   |   |   |   |  |  |

|         | Initial Value | 0 | 1        | 0 | 1 | 0 | 0 | 0 | 1 |  |  |

Bit 7~0 Reserved, must be [0b01010001]

#### • CFG10: Configuration Control Register10

| Address | Bit           | 7 | 6       | 5     | 4 | 3          | 2 | 1 | 0 |  |  |

|---------|---------------|---|---------|-------|---|------------|---|---|---|--|--|

|         | Name          |   | D_K     | [3:0] |   | TXPWR[3:0] |   |   |   |  |  |

| 0Ah     | R/W           |   | R/W R/W |       |   |            |   |   |   |  |  |

|         | Initial Value | 0 | 0       | 1     | 1 | 1          | 0 | 0 | 0 |  |  |

Bit 7~4 **D\_K[3:0]**: Fractional of dividend for MMD, which will be described later.

#### Bit 3~0 **TXPWR[3:0]**: RF output power stage selection

The device has several output power values which are 0, 5, 10 and 13dBm.

| TXPWR[3:0]   | RF Output Power (Typ.) |

|--------------|------------------------|

| <u>00</u> 00 | 0dBm                   |

| <u>01</u> 00 | 5dBm                   |

| <u>10</u> 00 | 10dBm                  |

| <u>11</u> 00 | 13dBm                  |

| TXPWR[3:0]   | Fine Tune Level (Typ.) |

|--------------|------------------------|

| XX <u>00</u> | 0                      |

| XX <u>01</u> | 1                      |

| XX <u>10</u> | 2                      |

| XX <u>11</u> | 3                      |

Note that the adjusting range: Level 3 > Level 2 > Level 1 > Level 0

### • CFG11: Configuration Control Register11

| Address | Bit           | 7 | 6                     | 5 | 4 | 3 | 2 | 1 | 0 |  |

|---------|---------------|---|-----------------------|---|---|---|---|---|---|--|

|         | Name          |   | D_N[5:0] BAND_SEL[1:0 |   |   |   |   |   |   |  |

| 0Bh     | R/W           |   | R/W                   |   |   |   |   |   |   |  |

|         | Initial Value | 0 | 1                     | 0 | 1 | 1 | 0 | 0 | 1 |  |

Bit 7~2 **D\_N[5:0]**: Integer of dividend for MMD

### Bit 1~0 BAND\_SEL[1:0]: Band Frequency Coarse Selection

| BAND_SEL | Frequency | Divider |

|----------|-----------|---------|

| 00       | 315MHz    | 2       |

| 01       | 433MHz    | 2       |

| 10       | 868MHz    | 1       |

| 11       | 915MHz    | 1       |

Note that the BAND\_SEL only selects an approximate frequency range while the exact frequency value is determined by the D\_N and D\_K bit fields. For example, the 433.92MHz belongs to 433MHz frequency band in the BAND\_SEL setting.

Rev. 1.81 15 October 29, 2021

### • CFG12: Configuration Control Register12

| Address | Bit           | 7 | 6         | 5 | 4 | 3 | 2 | 1 | 0 |  |  |

|---------|---------------|---|-----------|---|---|---|---|---|---|--|--|

|         | Name          |   | D_K[11:4] |   |   |   |   |   |   |  |  |

| 0Ch     | R/W           |   | R/W       |   |   |   |   |   |   |  |  |

|         | Initial Value | 0 | 1         | 1 | 1 | 0 | 0 | 0 | 0 |  |  |

### • CFG13: Configuration Control Register13

| Address | Bit           | 7 | 6          | 5 | 4 | 3 | 2 | 1 | 0 |  |  |

|---------|---------------|---|------------|---|---|---|---|---|---|--|--|

|         | Name          |   | D_K[19:12] |   |   |   |   |   |   |  |  |

| 0Dh     | R/W           |   | R/W        |   |   |   |   |   |   |  |  |

|         | Initial Value | 0 | 0          | 1 | 1 | 1 | 1 | 0 | 1 |  |  |

D\_K[19:0]: 20-bit fractional of dividend for MMD

For example: XO=16MHz and TX frequency band=433MHz

1. For D\_N field, (433M×Divider)/16M=54.125,

Take the integer part  $\rightarrow$  D\_N[5:0]=54-32=22=010110b

2. For D K field, (433M×Divider)/16M=54.125,

Take the fractional part  $\rightarrow$  D\_K[19:0]=0.125  $\times$  2<sup>20</sup>=131072=0010-0000-0000-0000-0000b

| Frequency | Divider | X'TAL | D_N[5:0]                   | D_K[19:4]           | D_K[3:0] |

|-----------|---------|-------|----------------------------|---------------------|----------|

| 315MHz    | 2       | 16MHz | 000111 0110-0000-0000-0000 |                     | 0000     |

| 433MHz    | 2       | 16MHz | 010110                     | 0010-0000-0000-0000 | 0000     |

| 433.92MHz | 2       | 16MHz | 010110                     | 0011-1101-0111-0000 | 1010     |

| 868MHz    | 1       | 16MHz | 010110                     | 0100-0000-0000-0000 | 0000     |

| 915MHz    | 1       | 16MHz | 011001                     | 0011-0000-0000-0000 | 0000     |

### • CFG14: Configuration Control Register14

| Addres | ss | Bit           | 7 | 6  | 5           | 4              | 3   | 2 | 1 | 0 |

|--------|----|---------------|---|----|-------------|----------------|-----|---|---|---|

|        |    | Name          |   | 00 | K Bit Rate[ | LEAD_CODE[2:0] |     |   |   |   |

| 0Eh    |    | R/W           |   |    | R/W         |                | R/W |   |   |   |

|        |    | Initial Value | 0 | 0  | 1           | 0              | 1   | 0 | 0 | 1 |

Bit 7~3 **OOK Bit Rate[4:0]**: Define the data bit rate (0.5k~6kbps)

| OOK Bit Rate | Data Rate | t <sub>DW</sub> |

|--------------|-----------|-----------------|

| 00000        | 0.5kbps   | 2ms             |

| 00001        | 0.6kbps   | 1.67ms          |

| 00010        | 0.7kbps   | 1.43ms          |

| 00011        | 0.8kbps   | 1.25ms          |

| 00100        | 0.9kbps   | 1.11ms          |

| 00101        | 1.0kbps   | 1ms             |

| 00110        | 1.1kbps   | 0.91ms          |

| 00111        | 1.2kbps   | 0.83ms          |

| 01000        | 1.3kbps   | 0.77ms          |

| 01001        | 1.4kbps   | 0.72ms          |

| 01010        | 1.5kbps   | 0.667ms         |

| 01011        | 1.6kbps   | 0.625ms         |

| 01100        | 1.7kbps   | 0.59ms          |

| 01101        | 1.8kbps   | 0.55ms          |

| 01110        | 1.9kbps   | 0.53ms          |

| 01111        | 2.0kbps   | 0.5ms           |

| OOK Bit Rate | Data Rate | t <sub>DW</sub> |

|--------------|-----------|-----------------|

| 10000        | 2.1kbps   | 0.476ms         |

| 10001        | 2.2kbps   | 0.454ms         |

| 10010        | 2.3kbps   | 0.434ms         |

| 10011        | 2.4kbps   | 0.416ms         |

| 10100        | 2.5 kbps  | 0.4ms           |

| 10101        | 2.6kbps   | 0.384ms         |

| 10110        | 2.7kbps   | 0.37ms          |

| 10111        | 2.8kbps   | 0.357ms         |

| 11000        | 2.9kbps   | 0.344ms         |

| 11001        | 3.0kbps   | 0.333ms         |

| 11010        | 3.5kbps   | 0.285ms         |

| 11011        | 4.0kbps   | 0.25ms          |

| 11100        | 4.5kbps   | 0.222ms         |

| 11101        | 5.0kbps   | 0.2ms           |

| 11110        | 5.5kbps   | 0.181ms         |

| 11111        | 6.0kbps   | 0.166ms         |

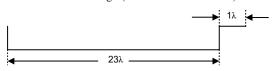

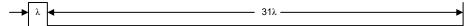

### Bit 2~0 LEAD\_CODE[2:0]: Define the lead code

000: 23λLow + 1λHigh (HT6P20B/HT6P2x7A)

001:  $1\lambda$ High +  $31\lambda$ Low (HT6P4x7A)

010:  $36\lambda$ Low +  $1\lambda$ High (HT12E)

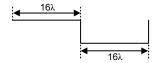

011: 16λHigh+ 16λLow

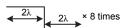

100:  $(1\lambda High + 1\lambda Low) \times 8$  times, 16 symbols in total

101:  $(2\lambda High + 2\lambda Low) \times 8$  times, 16 symbols in total

110:  $(1\lambda High + 1\lambda Low) \times 12$  times, 24 symbols in total

111:  $(2\lambda High + 2\lambda Low) \times 12$  times, 24 symbols in total

### • CFG15: Configuration Control Register15

| Address | Bit           | 7             | 6 | 5 | 4     | 3                          | 2  | 1        | 0        |

|---------|---------------|---------------|---|---|-------|----------------------------|----|----------|----------|

|         | Name          | ADDR_LEN[2:0] |   |   | END_C | D_CODE[1:0] START_BIT[1:0] |    | BIT[1:0] | Waveform |

| 0Fh     | R/W           | R/W           |   |   | R/    | W                          | R/ | W        | R/W      |

|         | Initial Value | 0             | 1 | 1 | 0     | 0                          | 0  | 0        | 1        |

Bit 7~5 ADDR\_LEN[2:0]: Define the address length

| ADDR_LEN                 | Format  |

|--------------------------|---------|

| 000 (HT12E)              | 8 bits  |

| 001                      | 12 bits |

| 010                      | 16 bits |

| 011 (HT6P427A)           | 20 bits |

| 100 (HT6P20B, HT6P237A)  | 22 bits |

| 101 (HT6P247A, HT6P437A) | 24 bits |

| 110                      | 28 bits |

| 111                      | 32 bits |

#### Bit 4~3 **END\_CODE[1:0]**: Define the End code

| END_CODE                         | Format                                          |

|----------------------------------|-------------------------------------------------|

| 00                               | Disable                                         |

| 01 (HT6P20B, HT6P237A, HT6P247A) | (1λ Low + 2λ High + 2λ Low + 1λ High) × 2=(12λ) |

| 10                               | 4λ <sup>(Note 1)</sup>                          |

| 11                               | 2λ + 2λ <sup>(Note 2)</sup>                     |

#### Notes:

- 1. The high or low level of the  $4\lambda$  END CODE is the opposite of the previous symbol level.

- Example 1: Clear the Waveform to "0", no matter that whether the data is "1" or "0", the last symbol will be High, here the  $4\lambda$  must be  $4\lambda$  Low.

| Pilot(24 λ) Address(22-bit) | Data(2-bit) | End(4 λ) |

|-----------------------------|-------------|----------|

|-----------------------------|-------------|----------|

Pilot code is  $24\lambda \rightarrow \text{LEAD CODE}[2:0]=000b$ ;

Address: [155555h]; Address length is 22-bit  $\rightarrow$  ADDR\_LEN[2:0]=100b;

DATA: 2 Keys (D1/D0)  $\rightarrow$  KEY SEL[1:0]=00b;

End code is 4-bit  $\rightarrow$  END\_CODE[1:0]=10b;

Bit format: Low to High  $\rightarrow$  Waveform=0b;

$1\lambda \text{ Low} + 2\lambda \text{ High (Data=Zero)} / 2\lambda \text{ Low} + 1\lambda \text{ High (Data=One)}$

- Example 2: Set the Waveform to "1", no matter whether the data is "1" or "0", the last symbol will be Low, here the  $4\lambda$  must be  $4\lambda$  High.

- 2.  $2\lambda + 2\lambda$ : these two  $2\lambda$  are opposite to each other, while the high or low level of the first  $2\lambda$  is opposite to the previous symbol level.

- Example 1: Clear the Waveform to "0", no matter whether the data is "1" or "0", the last symbol will be High, and here the  $2\lambda + 2\lambda$  must be  $2\lambda \text{ Low} + 2\lambda \text{ High}$ .

| Pilot(24 λ) | Address(22-bit) | Data(2-bit) | End(2 λ+2 λ) |

|-------------|-----------------|-------------|--------------|

Pilot code is  $24\lambda \rightarrow \text{LEAD CODE}[2:0]=000b$ ;

Address: [155555h]; Address length is 22-bit  $\rightarrow$  ADDR LEN[2:0]=100b;

DATA: 2 Keys (D1/D0)  $\rightarrow$  KEY\_SEL[1:0]=00b;

End code is 4-bit  $\rightarrow$  END CODE[1:0]=11b;

Bit format: Low to High → Waveform=0b;

$1\lambda \text{ Low} + 2\lambda \text{ High (Data=Zero)} / 2\lambda \text{ Low} + 1\lambda \text{ High (Data=One)}$

Example 2: Set the Waveform to "1", no matter that the data is "1" or "0", the last symbol will be Low, and here the 2λ + 2λ must be 2λ High + 2λ Low.

Rev. 1.81 18 October 29, 2021

### Bit 2~1 START\_BIT[1:0]: Only for OOK Encoder

| START_BIT | Format             |

|-----------|--------------------|

| 00        | Disable            |

| 01        | (2λ Low + 4λ High) |

| 10        | (4λ High + 2λ Low) |

| 11        | 6λ Low             |

#### Bit 0 Waveform:

### • CFG16: Configuration Control Register16

| Address | Bit           | 7        | 6       | 5        | 4 | 3            | 2 | 1            | 0 |

|---------|---------------|----------|---------|----------|---|--------------|---|--------------|---|

|         | Name          | Reserved | Encoder | Reserved |   | CRC_SEL[1:0] |   | KEY_SEL[1:0] |   |

| 10h     | R/W           | R/W      | R/W     | R/W      |   | R/           | W | R/           | W |

|         | Initial Value | 1        | 0       | 0        | 0 | 0            | 0 | 0            | 1 |

Bit 7 Reserved, must be [0b1]

Bit 6 **Encoder**: Mode selection

0: I<sup>2</sup>C Mode 1: Key Mode

Bit 5~4 Reserved, must be [0b00]

#### Bit 3~2 CRC\_SEL[1:0]: Select the address + data for CRC processing

The unit is Bit (not  $\lambda$ ), the address is used as the high order of CRC polynomial and the data is used as the low order.

| CRC_SEL | Format                                                     | Polynomial | Initial Value | Note |

|---------|------------------------------------------------------------|------------|---------------|------|

| 00      | Disable                                                    | _          | _             | OOK  |

| 01      | 4 Bits → Take the low nibble of the CRC8 calculated result | _          | _             | ООК  |

| 10      | 8 Bits $\to X^8 + X^5 + X^4 + 1$                           | 0x31       | 0x00          | OOK  |

| 11      | Reserved                                                   | _          | _             | _    |

#### Bit 1~0 **KEY\_SEL[1:0]**

| KEY_SEL | Format                 | Data bits                                    |

|---------|------------------------|----------------------------------------------|

| 00      | 2 Keys                 | 2 bits                                       |

| 01      | 4 Keys                 | 4 bits                                       |

| 10      | 4 Dipswitches + 4 Keys | 4 bits (4-bit external address + 4-bit data) |

| 11      | 8 Keys                 | 8 bits                                       |

For the 16-pin package type, in the Key mode:

- 1. If this bit field is set as "00" then to select Keys D0~D1, the other 6 keys D2~D7 have no trigger function;

- 2. If the value is "01" then to select Keys D0~D3, the other 4 keys D4~D7 have no trigger function;

- 3. If the value is "10" then to select 4 Dipswitches + 4 Keys, the 4 dipswitch I/O status will be latched after power on, the dipswitches will maintain a pull-high or pull low status according to the latched high or low level to avoid current leakage in the Deep Sleep mode. These four dipswitches D4~D7 have no trigger function but will affect the address.

- 4. If dipswitch ever been changed, it is recommended to re-trigger key or re-power on.

In the I<sup>2</sup>C Mode, the TX transmitting data is determined by the I<sup>2</sup>C\_DATA bit field while the transmitting data bit format is determined by the KEY SEL bit field. The Data bit formats is shown as below:

| I <sup>2</sup> C Mode | оок       |

|-----------------------|-----------|

| 2 Keys                | xx        |

| 4 Keys                | xxxx      |

| 4 + 4 Keys            | AAAAxxxx  |

| 8 Keys                | xxxx_xxxx |

For 2-key/4-key/8-key configurations the data bit can be 2 bits, 4 bits and 8 bits respectively. As the above table shows, if the KEY\_SEL bit field is set as "10" to select 4 Dipswitches + 4 Keys, then I2C will transmit 8-bit data (bit  $7 \sim$  bit 0) and the bit  $7 \sim$  bit 4 is regarded as Address.

In the Key Mode, the TX transmitting data is determined by the keys while the transmitting data bit format is determined by the KEY SEL bit field. The Data bit formats is shown as below:

| Key Mode   | оок       |

|------------|-----------|

| 2 Keys     | xx        |

| 4 Keys     | xxxx      |

| 4 + 4 Keys | AAAAxxxx  |

| 8 Keys     | xxxx_xxxx |

As the above table shows, if the KEY\_SEL bit field is set as "10" to select 4 Dipswitches + 4 Keys, the value of "A" is determined by Dipswitches and have no TX transmit trigger function. The data bit format can be 2 bits, 4 bits and 8 bits when the KEY\_SEL bit field is configured to select 2 keys, 4 keys and 8 keys respectively. When the bit field is set to select 4 Dipswitches + 4 Keys, then the low nibble, bit 3~bit 0, is regarded as data and the 4-bit Dipswitches values is regarded as address.

Rev. 1.81 20 October 29, 2021

LSB MSB Internal Address

| LSB |    |        |         |    |         |            |        | MS      | 3        |    |     |    |

|-----|----|--------|---------|----|---------|------------|--------|---------|----------|----|-----|----|

|     | lr | nterna | l Addre | ss | Externa | al Address | s (dip | switch) |          | D  | ATA |    |

|     | A0 | A1     | ~       | An | An+0    | An+1 A     | n+2    | An+3    |          | D2 | D1  | D0 |

|     |    |        |         |    |         |            |        |         | or<br>D0 | D1 | D2  | D3 |

• HT6P427A

| Pilot-code | A0~A19 | D0~D3 |

|------------|--------|-------|

|------------|--------|-------|

• HT6P437A

Pilot-code A0~A23 D0~D3

• HT6P237A

Pilot-code A0~A21 D1~D0 "0101"

• HT6P247A

Pilot-code A0~A23 D3~D0 "0101"

• HT6P20B

Pilot-code A0~A21 D1~D0 "0101"

• HT12E2Tx

Pilot-code A0~A7 D0~D3

### • CFG17: Configuration Control Register17

| Address | Bit           | 7   | 6        | 5 | 4 | 3 | 2 | 1 | 0 |  |

|---------|---------------|-----|----------|---|---|---|---|---|---|--|

|         | Name          |     | Reserved |   |   |   |   |   |   |  |

| 11h     | R/W           | R/W |          |   |   |   |   |   |   |  |

|         | Initial Value | 1   | 0        | 1 | 1 | 0 | 0 | 0 | 0 |  |

### • CFG18: Configuration Control Register18

| Address | Bit           | 7 | 6        | 5 | 4  | 3 | 2 | 1 | 0 |  |  |

|---------|---------------|---|----------|---|----|---|---|---|---|--|--|

|         | Name          |   | Reserved |   |    |   |   |   |   |  |  |

| 12h     | R/W           |   |          |   | R/ | W |   |   |   |  |  |

|         | Initial Value | 1 | 0        | 1 | 1  | 0 | 0 | 0 | 1 |  |  |

### • CFG19: Configuration Control Register19

| Address | Bit           | 7 | 6        | 5 | 4  | 3 | 2 | 1 | 0 |  |

|---------|---------------|---|----------|---|----|---|---|---|---|--|

|         | Name          |   | Reserved |   |    |   |   |   |   |  |

| 13h     | R/W           |   |          |   | R/ | W |   |   |   |  |

|         | Initial Value | 1 | 0        | 1 | 1  | 0 | 0 | 1 | 0 |  |

### • CFG20: Configuration Control Register20

| Address | Bit           | 7 | 6        | 5 | 4  | 3 | 2 | 1 | 0 |  |

|---------|---------------|---|----------|---|----|---|---|---|---|--|

|         | Name          |   | Reserved |   |    |   |   |   |   |  |

| 14h     | R/W           |   |          |   | R/ | W |   |   |   |  |

|         | Initial Value | 1 | 0        | 1 | 1  | 0 | 0 | 1 | 1 |  |

The CFG17~CFG20 are reserved registers, whose default value must be fixed as 0xB0, 0xB1, 0xB2 and 0xB3 respectively.

Rev. 1.81 21 October 29, 2021

### • CFG21: Configuration Control Register21

| Address | Bit           | 7 | 6                  | 5 | 4  | 3 | 2 | 1 | 0 |  |  |

|---------|---------------|---|--------------------|---|----|---|---|---|---|--|--|

|         | Name          |   | ENCODER_ADDRL[7:0] |   |    |   |   |   |   |  |  |

| 15h     | R/W           |   |                    |   | R/ | W |   |   |   |  |  |

|         | Initial Value | 0 | 0                  | 0 | 0  | 0 | 0 | 0 | 0 |  |  |

#### • CFG22: Configuration Control Register22

| Address | Bit           | 7 | 6                  | 5 | 4  | 3 | 2 | 1 | 0 |  |

|---------|---------------|---|--------------------|---|----|---|---|---|---|--|

|         | Name          |   | ENCODER_ADDRM[7:0] |   |    |   |   |   |   |  |

| 16h     | R/W           |   |                    |   | R/ | W |   |   |   |  |

|         | Initial Value | 0 | 0                  | 0 | 0  | 0 | 0 | 0 | 0 |  |

#### • CFG23: Configuration Control Register23

| Address | Bit           | 7 | 6                  | 5 | 4 | 3 | 2 | 1 | 0 |  |  |

|---------|---------------|---|--------------------|---|---|---|---|---|---|--|--|

|         | Name          |   | ENCODER_ADDRH[7:0] |   |   |   |   |   |   |  |  |

| 17h     | R/W           |   | R/W                |   |   |   |   |   |   |  |  |

|         | Initial Value | 0 | 0                  | 0 | 0 | 0 | 0 | 0 | 0 |  |  |

### • CFG24: Configuration Control Register24

| Address | Bit           | 7 | 6                  | 5 | 4  | 3 | 2 | 1 | 0 |  |  |

|---------|---------------|---|--------------------|---|----|---|---|---|---|--|--|

|         | Name          |   | ENCODER_ADDRU[7:0] |   |    |   |   |   |   |  |  |

| 18h     | R/W           |   |                    |   | R/ | W |   |   |   |  |  |

|         | Initial Value | 0 | 0 0 0 0 0 0 0 0    |   |    |   |   |   |   |  |  |

The CFG21~CFG24 define the encoder address.

### • CFG25: Configuration Control Register25

| Address              | Bit           | 7 | 6 | 5 | 4  | 3 | 2 | 1 | 0 |

|----------------------|---------------|---|---|---|----|---|---|---|---|

| Name FRAME_CNTR[7:0] |               |   |   |   |    |   |   |   |   |

| 19h                  | R/W           |   |   |   | R/ | W |   |   |   |

|                      | Initial Value | 0 | 0 | 0 | 0  | 0 | 0 | 0 | 0 |

### Bit 7~0 **FRAME\_CNTR[7:0]**

The Frame Counter calculates the frame numbers using the following equation:

$CNTR = FRAME\_CNTR[7:0] + 1$

0000: Transmit 1 complete frame

0001: Transmit 2 complete frames

0010: Transmit 3 complete frames

:

1111: Transmit 16 complete frames

### • CFG26: Configuration Control Register26

| Address     | Bit           | 7 | 6 | 5 | 4 | 3 | 2 | 1 | 0 |

|-------------|---------------|---|---|---|---|---|---|---|---|

|             | Name Reserved |   |   |   |   |   |   |   |   |

| 1Ah R/W R/W |               |   |   |   |   |   |   |   |   |

|             | Initial Value | 0 | 0 | 0 | 0 | 0 | 1 | 1 | 1 |

Bit 7~0 Reserved, must be [0b00000111]

Rev. 1.81 22 October 29, 2021

#### CFG27: Configuration Control Register27

| Address | Bit           | 7 | 6        | 5 | 4  | 3 | 2 | 1 | 0 |  |  |

|---------|---------------|---|----------|---|----|---|---|---|---|--|--|

|         | Name          |   | Reserved |   |    |   |   |   |   |  |  |

| 1Bh     | R/W           |   |          |   | R/ | W |   |   |   |  |  |

|         | Initial Value | 0 | 0        | 0 | 0  | 1 | 0 | 0 | 0 |  |  |

Bit 7~0 Reserved, must be [0b00001000]

### • CFG28 : Configuration Control Register28

| Address | Bit           | 7        | 6       | 5       | 4       | 3        | 2 | 1 | 0 |

|---------|---------------|----------|---------|---------|---------|----------|---|---|---|

|         | Name          | Reserved | TXD_INV | TXD_REV | LED_SWD | Reserved |   |   |   |

| 1Ch     | R/W           | R/W      | R/W     | R/W     | R/W     | R/W      |   |   |   |

|         | Initial Value | 0        | 0       | 0       | 0       | 0        | 0 | 0 | 0 |

Bit 7 Reserved, must be [0b0]

Bit 6 **TXD\_INV**: data inverse

0: No inverse. If key trigger, data will be "1".

1: DATA "0" will be inversed as "1" and vice versa. If key trigger, data will be "0".

Bit 5 TXD\_REV: Data MSB and LSB reverse control

| 0: | LSB                             | MSB                         |      |    |    |    |  |  |  |  |

|----|---------------------------------|-----------------------------|------|----|----|----|--|--|--|--|

|    | Internal Address (ENCODER_ADDR) | External Address(dipswitch) |      |    |    |    |  |  |  |  |

|    |                                 |                             | D0   | D1 | D2 | D3 |  |  |  |  |

| 1: | LSB                             | MSB                         |      |    |    |    |  |  |  |  |

|    | Internal Address (ENCODER_ADDR) | External Address(dipswitch) | Data |    |    |    |  |  |  |  |

|    | ·                               |                             | D3   | D2 | D1 | D0 |  |  |  |  |

Bit 4 **LED\_SWD**: LED switch

0: LED follows the TX

1: LED follows the symbol high

Bit 3~0 Reserved, must be [0b0000]

#### • CFG30: Configuration Control Register30

| Address | Bit           | 7 | 6             | 5 | 4  | 3 | 2 | 1 | 0 |  |  |

|---------|---------------|---|---------------|---|----|---|---|---|---|--|--|

|         | Name          |   | MAX_FCNT[7:0] |   |    |   |   |   |   |  |  |

| 1Eh     | R/W           |   |               |   | R/ | W |   |   |   |  |  |

|         | Initial Value | 0 | 0             | 0 | 0  | 0 | 0 | 0 | 0 |  |  |

### Bit 7~0 **MAX\_FCNT[7:0]**

The TX will be disabled when the Frame Counter stops. However this bit field is used for the counted frames multiplication. This function is disabled when the bit field value is "0", otherwise the keys should be pressed and hold for a maximum waiting time to disable the TX, where the maximum waiting time =  $(FRAME\_CNTR[7:0]+1) \times MAX\_FCNT[7:0]$

The TX will be disabled when the Frame Counter stops. This feature can be used to prevent battery exhaust due to continued transmission made by jammed button.

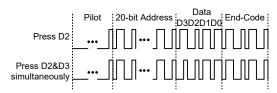

BC2161 Frame (HT6P20B packet format)

Bit format:

$1\lambda \text{ low} + 2\lambda \text{ high} \rightarrow \text{Data} = \text{Zero}$

$2\lambda \text{ low} + 1\lambda \text{ high} \rightarrow \text{Data} = \text{One}$

Data Rate: 1kbps

$1\lambda \text{ Time: } 1\text{ms/3} = 0.3333\text{ms}$

Numbers of  $\lambda$  in a frame  $\rightarrow$  28-bit  $\times$  3 $\lambda$  + 24 $\lambda$  = 108 $\lambda$

1 Frame time  $\rightarrow$  108 $\lambda \times$  0.3333ms = 35.9964ms

Example 1:

$FRAME\_CNTR[7:0] = 03b \rightarrow Frame 1 / Frame 2 / Frame 3 / Frame 4$

MAX FCNT[7:0] = 00b

#### Example 2:

FRAME CNTR[7:0]=  $00b \rightarrow Frame 1$

MAX FCNT[7:0] = 04b

When stuck key occurs, the power consumption caused by Tx continuous transmission can be avoided by setting the MAX FCNT[7:0] bits.

Total Frame Numbers =  $(FRAME\ CNTR[7:0]+1) \times MAX\ FCNT[7:0]$

### • CFG31: Configuration Control Register31

| Address | Bit           | 7 | 6             | 5 | 4  | 3 | 2 | 1 | 0 |  |  |

|---------|---------------|---|---------------|---|----|---|---|---|---|--|--|

|         | Name          |   | EFCRC_L[7:0]  |   |    |   |   |   |   |  |  |

| 1Fh     | R/W           |   |               |   | R/ | W |   |   |   |  |  |

|         | Initial Value | 0 | 0 0 0 0 0 0 0 |   |    |   |   |   |   |  |  |

### • CFG32: Configuration Control Register32

| Address | Bit           | 7            | 6             | 5 | 4 | 3 | 2 | 1 | 0 |  |

|---------|---------------|--------------|---------------|---|---|---|---|---|---|--|

|         | Name          | EFCRC_H[7:0] |               |   |   |   |   |   |   |  |

| 20h     | R/W           |              | R/W           |   |   |   |   |   |   |  |

|         | Initial Value | 0            | 0 0 0 0 0 0 0 |   |   |   |   |   |   |  |

EFCRC field: for FUSE CRC calculation

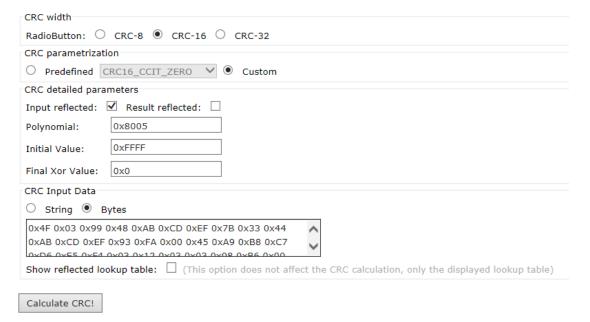

The address range of the CRC calculation is from 00h to 1Eh, which contains 31 bytes in total. The input order is LSB first, the CRC polynomial is  $X^{16} + X^{15} + X^2 + 1$ . The CRC on-line calculator can be accessed by the following website: <a href="http://www.sunshine2k.de/coding/javascript/crc/crc\_is.html">http://www.sunshine2k.de/coding/javascript/crc/crc\_is.html</a>

Rev. 1.81 24 October 29, 2021

For example:

Data filled in the address range of 00h~1Eh are listed below:

$0x4F\ 0x03\ 0x99\ 0x48\ 0xAB\ 0xCD\ 0xEF\ 0x7B\ 0x33\ 0x44\ 0xAB\ 0xCD\ 0xEF\ 0x93\ 0xFA\ 0x00\ 0x45\ 0xA9\ 0xB8\\ 0xC7\ 0xD6\ 0xE5\ 0xF4\ 0x03\ 0x12\ 0x03\ 0x03\ 0x08\ 0xB6\ 0x00\ 0x00$

The online calculator should be setup with the following configuration:

- 1. CRC width: select "CRC-16"

- 2. CRC parametrization: select "Custom"

- 3. CRC detailed parameters: select "Input reflected"

- 4. Polynomial: 0x80055. Initial Value: 0xFFFF6. Final Xor Value: 0x0

- 7. CRC Input Data: select "Bytes" and fill in the data

- 8. Click on "Calculate CRC!"9. Result CRC Value: 0x768C

As the following on-line calculator web interface screenshot shows:

Result CRC value: 0x768C

#### • CFG33: Configuration Control Register33

| Address | Bit           | 7             | 6 | 5 | 4        | 3 | 2 | 1 | 0       |

|---------|---------------|---------------|---|---|----------|---|---|---|---------|

|         | Name          |               |   |   | Reserved |   |   |   | TX_FLAG |

| 21h     | Ih R/W R/W    |               |   |   |          |   | R |   |         |

|         | Initial Value | 0 0 0 0 0 0 0 |   |   |          |   |   |   |         |

#### Bit 7~1 Reserved, must be [0b0000000]

### Bit 0 **TX\_FLAG**: Transmission flag

- 0: Transmission is in progress, LED on

- 1: No transmission, LED off

### • CFG40: Configuration Control Register 40

| Address | Bit           | 7 | 6                          | 5 | 4 | 3   | 2 | 1 | 0 |  |  |  |

|---------|---------------|---|----------------------------|---|---|-----|---|---|---|--|--|--|

|         | Name          |   | I <sup>2</sup> C_DATA[7:0] |   |   |     |   |   |   |  |  |  |

| 28h     | R/W           |   |                            |   | F | R/W |   |   |   |  |  |  |

|         | Initial Value | 0 | 0                          | 0 | 0 | 0   | 0 | 0 | 1 |  |  |  |

### Bit 7~0 I<sup>2</sup>C\_DATA[7:0]: Data and address to be transmitted in the I<sup>2</sup>C mode

As the I<sup>2</sup>C state machine shows, the TX transmission will only be initiated after the I<sup>2</sup>C\_DATA[7:0] field has been written and the I<sup>2</sup>C stop is executed. The relationship between this bit field and the KEY\_SEL field in the CFG16 is described as below:

- 1. If KEY\_SEL selects 2 Keys, the I<sup>2</sup>C will only transmit the data of bit 0 and bit 1, namely 2-bit data.

- 2. If KEY SEL selects 4 Keys, the I<sup>2</sup>C will only transmit the data of bit 0~bit 3, namely 4-bit data.

- 3. If KEY\_SEL selects 4 Dipswitches + 4 Keys, the I<sup>2</sup>C will transmit the data of bit 0~bit 7, so the 4-bit External Address (Bit 4~Bit 7) and 4-bit data (Bit 0~Bit 3).

- 4. If KEY SEL selects 8 Keys, the I<sup>2</sup>C will transmit the data of bit 0~bit 7, namely 8-bit data.

- 5. It should be noted that in the I<sup>2</sup>C mode, D0~D7 have no trigger function, the data is all determined by the I<sup>2</sup>C\_DATA bit field while the bit number is controlled by the KEY\_SEL bit field.

Rev. 1.81 26 October 29, 2021

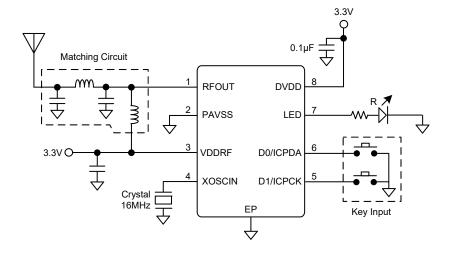

# **Application Circuits**

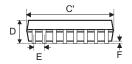

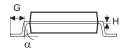

# **Package Information**

Note that the package information provided here is for consultation purposes only. As this information may be updated at regular intervals users are reminded to consult the <u>Holtek website</u> for the latest version of the <u>Package/Carton Information</u>.

Additional supplementary information with regard to packaging is listed below. Click on the relevant section to be transferred to the relevant website page.

- Package Information (include Outline Dimensions, Product Tape and Reel Specifications)

- The Operation Instruction of Packing Materials

- Carton information

Rev. 1.81 28 October 29, 2021

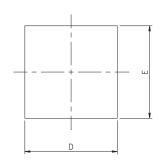

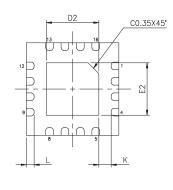

# 8-pin SOP-EP (150mil) Outline Dimensions

| Symbol | Dimensions in inch |           |       |

|--------|--------------------|-----------|-------|

|        | Min.               | Nom.      | Max.  |

| A      | _                  | 0.236 BSC | _     |

| В      | _                  | 0.154 BSC | _     |

| С      | 0.012              | _         | 0.020 |

| C'     | _                  | 0.193 BSC | _     |

| D      | _                  | _         | 0.069 |

| D1     | 0.076              | _         | 0.090 |

| E      | _                  | 0.050 BSC | _     |

| E2     | 0.076              | _         | 0.090 |

| F      | 0.000              | _         | 0.006 |

| G      | 0.016              | _         | 0.050 |

| Н      | 0.004              | _         | 0.010 |

| α      | 0°                 | _         | 8°    |

| Symbol | Dimensions in mm |          |      |

|--------|------------------|----------|------|

|        | Min.             | Nom.     | Max. |

| A      | _                | 6.00 BSC | _    |

| В      | _                | 3.90 BSC | _    |

| С      | 0.31             | _        | 0.51 |