2F, RiteKom Bldg No.669, Sec. 4, Chung Hsing Rd., Chutung, Hsinchu, Taiwan 310, R.O.C. Tel: 886-3-5833899-3001 or 1001 or 1005 Fax: 886-3-5833666

# **Phison PS3006 Controller**

Version 1.2

### **Contents**

- A. Features

- B. General Description

- C. Block Diagram

- **D.** Pin Configuration

- D1. TQFP/LQFP 100 pin (8CE) Configuration

- D2. TQFP/LQFP 100 pin (16CE) Configuration

- D3. BGA 85pin (8CE) Configuration

- E. Pin Description

- F. Power Consumption

- **G. Electrical Specifications**

- H. DC Characters

- I. AC Characters

- **I1. PCMCIA Interface**

- I2. IDE Interface

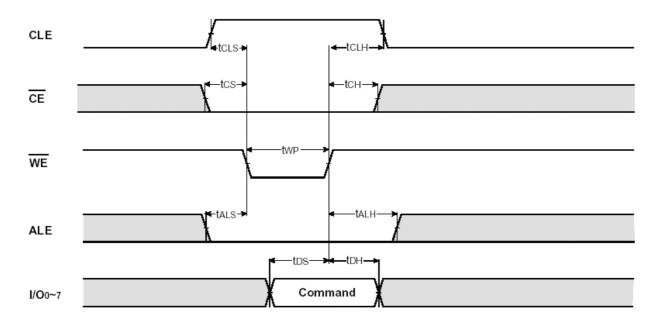

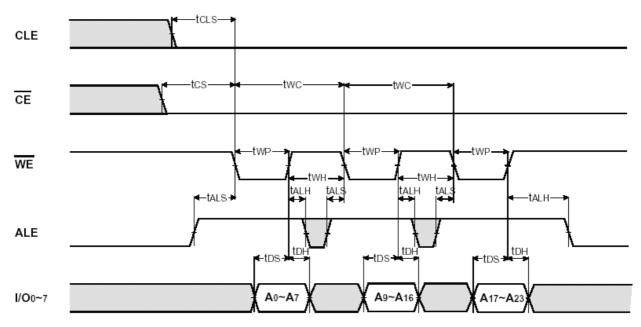

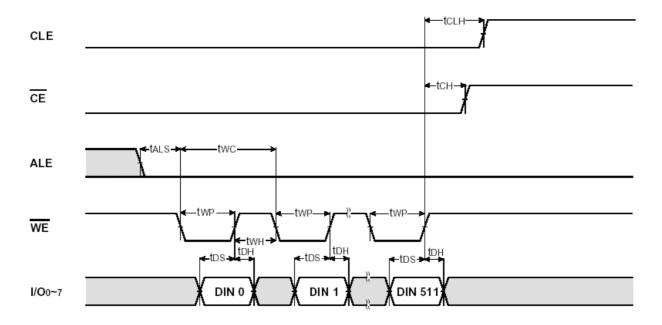

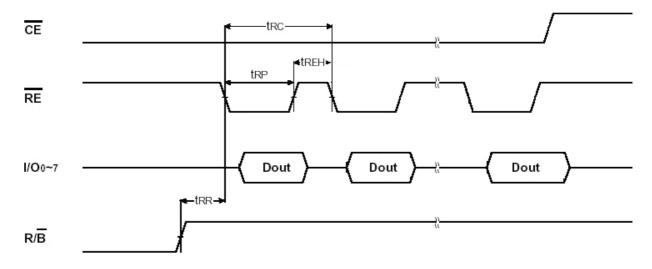

- **I3. Flash Interface**

- J. Package

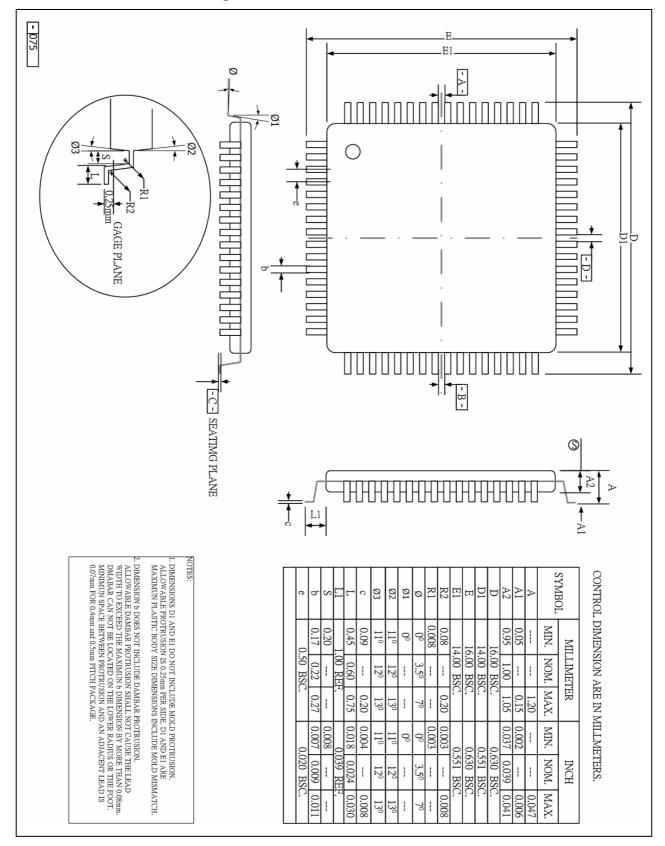

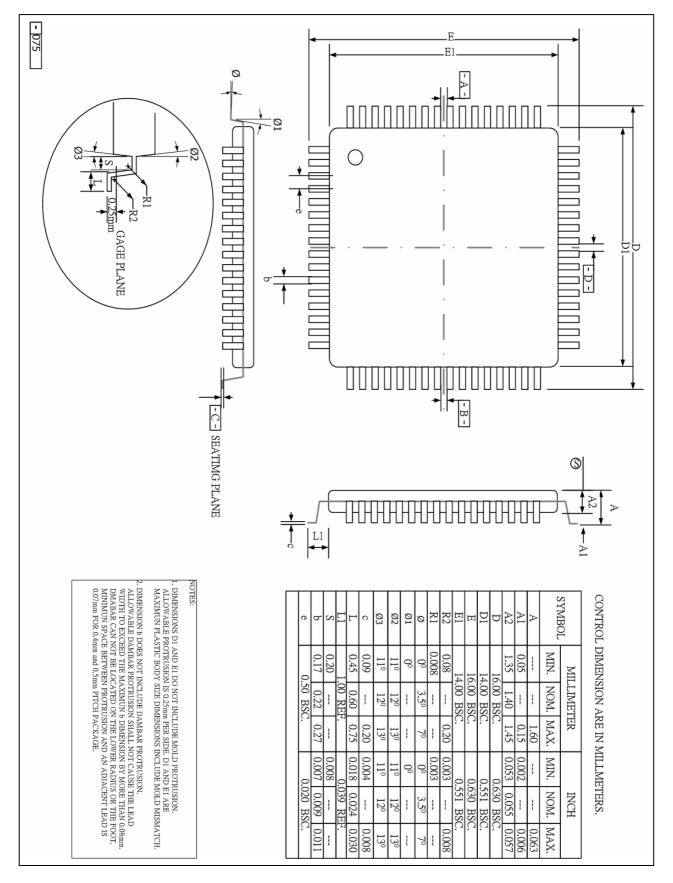

- J1. TQFP100

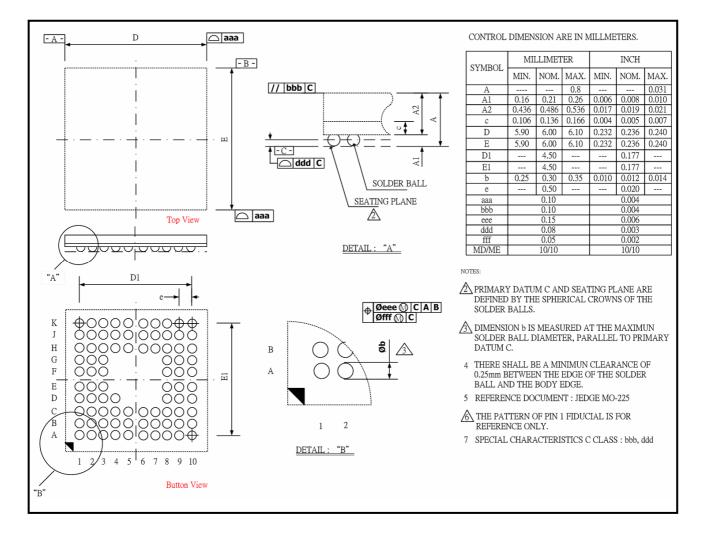

- J2. BGA85

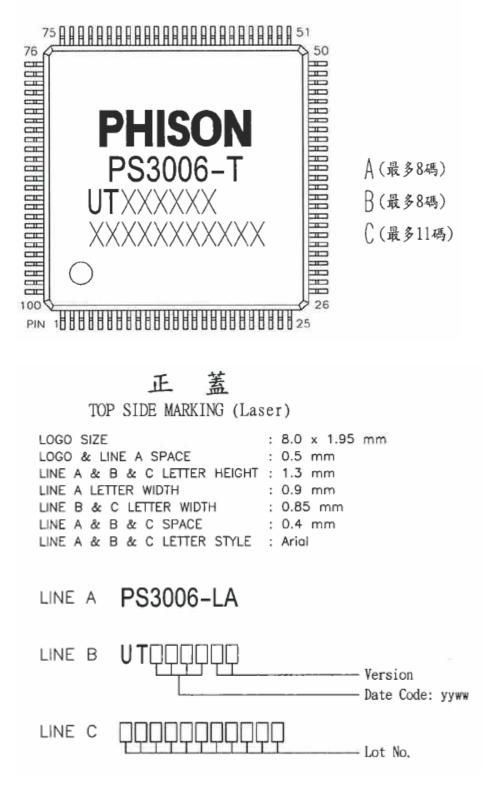

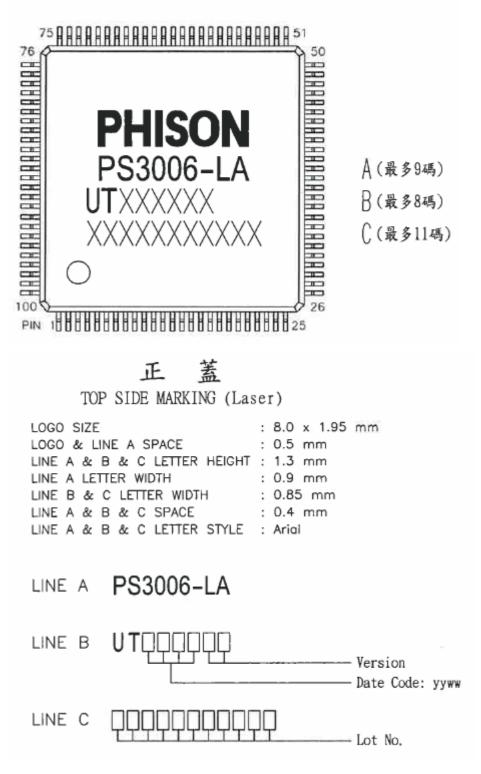

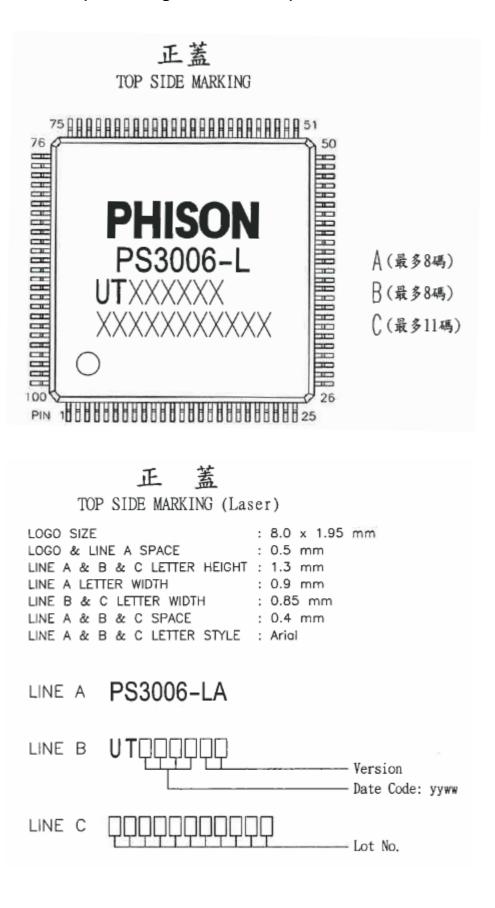

- K. PS3006 Marking

- K1. LQFP (LVDT=2.4V)

- K2. LQFP (LVDT=2.8V)

- K3. TQFP

### **Revision History**

| <b>Revision No</b> | History                                                        | Draft Date  |

|--------------------|----------------------------------------------------------------|-------------|

| 0.0                | 1. Initial issue                                               | Apr.10.2007 |

| 1.0                | Take out 128 pin package                                       | Oct.11,2007 |

| 1.1                | 1. Page3,Built-in hardware ECC circuit(Reed-Solomon)->(B.C.H.) | Nov.1,2007  |

|                    | 2. Page7, FCE7 -> FCE7-                                        |             |

|                    | Page11, B10 VSSK -> B10 VSS                                    |             |

|                    | 3. Pin Description add PU/PD field                             |             |

|                    | 4. add LQFP-100 Package                                        |             |

| 1.2 | 1. Page 44, 45, 46: Add marking information for PS3006 on different | Nov.14, 2007 |

|-----|---------------------------------------------------------------------|--------------|

|     | package                                                             |              |

|     |                                                                     |              |

## A. Features

### 1. Support Host Interfaces :

• PCMCIA/IDE Interface (Support to PIO Mode 6 & Multi Word DMA Mode4 & Ultra DMA Mode 6)

- Fully compatible with CompactFlash Specification Version 3.0

- Fully compatible with PC Card Standard Release 8.0

- Fully compatible with the IDE standard interface

- Host Transfer Rate for PC Card/CompactFlash : 25MB/s (PIO6)

- Host Transfer Rate for IDE standard interface: 133MB/s (UDMA6)

# 2. Build-In NAND Flash Memory Interface(support Individual mode, Dual mode and Quadruple mode)

- Build-in hardware ECC circuit (B.C.H.), support max 12 bit ECC.

- Support SLC(Single level cell) and MLC(Multi level cell) NAND Flash Memory

- Support 512B per page, 2KB per page, 4KB per page NAND Flash Memory

### 3. Build-In 1T RISC uP8051:

- 4. Build-In Oscillator:

- 5. Build-In Low Voltage Detector:

- 6. Build-In Regulator: 3.3V and 1.8V

- 7. 100-Pin TQFP/LQFP Package and 85-Ball BGA Package are available.

- 8. Operating Voltage: 2.7~5.5V

- 9. Power Saving implemented

## **B.** General Description

The PHISON PS3006 micro-controller is the best choice for CompactFlash<sup>™</sup> card and IDE interface storage devices. It is a powerful chip with excellent performance and low cost. All flash modules, commercial or industrial, designed in with this controller can exclude the mechanical parts which have the full advantage of anti vibration and extremely low power consumption. With built in regulator and oscillator, this reduces cost for external components. With the latest Program RAM and SMART commands integrated into this one chip solution, efforts from R/D to mass production will greatly decrease, at the same time, providing the edge to shortening time to market.

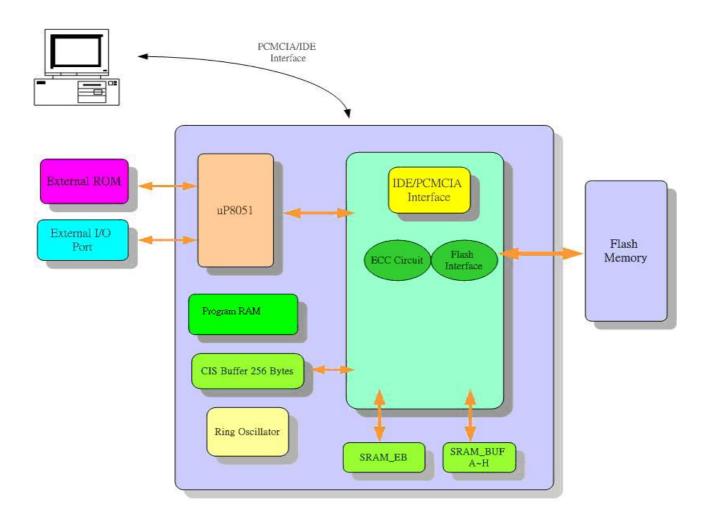

# C. Block Diagram

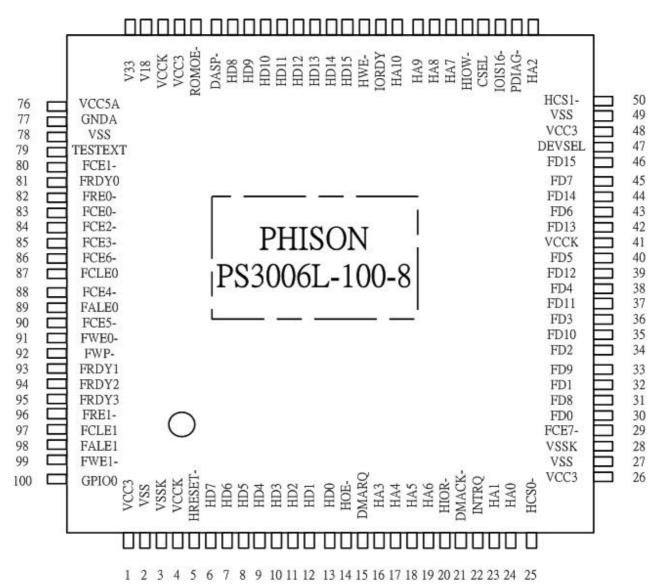

## D1. PACKAGE TYPE : TQFP/LQFP100 (8CE)

75 74 73 72 71 70 69 68 67 66 65 64 63 62 61 60 59 58 57 56 55 54 53 52 51

**PS3006**

| 1  | VCC3    | 26 | VCC3   | 51 | HA2     | 76  | VCC5A   |

|----|---------|----|--------|----|---------|-----|---------|

| 2  | VSS     | 27 | VSS    | 52 | PDIAG-  | 77  | GNDA    |

| 3  | VSSK    | 28 | VSSK   | 53 | IOIS16- | 78  | VSS     |

| 4  | VCCK    | 29 | FCE7-  | 54 | CSEL    | 79  | TESTEXT |

| 5  | HRESET- | 30 | FD0    | 55 | HIOW-   | 80  | FCE1-   |

| 6  | HD7     | 31 | FD8    | 56 | HA7     | 81  | FRDY0   |

| 7  | HD6     | 32 | FD1    | 57 | HA8     | 82  | FRE0-   |

| 8  | HD5     | 33 | FD9    | 58 | HA9     | 83  | FCE0-   |

| 9  | HD4     | 34 | FD2    | 59 | HA10    | 84  | FCE2-   |

| 10 | HD3     | 35 | FD10   | 60 | IORDY   | 85  | FCE3-   |

| 11 | HD2     | 36 | FD3    | 61 | HWE-    | 86  | FCE6-   |

| 12 | HD1     | 37 | FD11   | 62 | HD15    | 87  | FCLE0   |

| 13 | HD0     | 38 | FD4    | 63 | HD14    | 88  | FCE4-   |

| 14 | HOE-    | 39 | FD12   | 64 | HD13    | 89  | FALE0   |

| 15 | DMARQ   | 40 | FD5    | 65 | HD12    | 90  | FCE5-   |

| 16 | HA3     | 41 | VCCK   | 66 | HD11    | 91  | FWE0-   |

| 17 | HA4     | 42 | FD13   | 67 | HD10    | 92  | FWP-    |

| 18 | HA5     | 43 | FD6    | 68 | HD9     | 93  | FRDY1   |

| 19 | HA6     | 44 | FD14   | 69 | HD8     | 94  | FRDY2   |

| 20 | HIOR-   | 45 | FD7    | 70 | DASP-   | 95  | FRDY3   |

| 21 | DMACK-  | 46 | FD15   | 71 | ROMOE-  | 96  | FRE1-   |

| 22 | INTRQ   | 47 | DEVSEL | 72 | VCC3    | 97  | FCLE1   |

| 23 | HA1     | 48 | VCC3   | 73 | VCCK    | 98  | FALE1   |

| 24 | HA0     | 49 | VSS    | 74 | V18     | 99  | FWE1-   |

| 25 | HCS0-   | 50 | HCS1-  | 75 | V33     | 100 | GPIO0   |

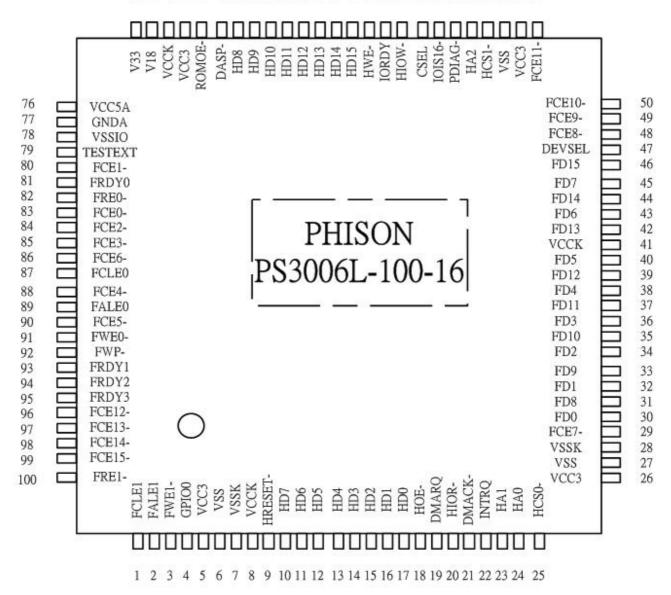

## D2. PACKAGE TYPE : TQFP/LQFP100 (16CE)

75 74 73 72 71 70 69 68 67 66 65 64 63 62 61 60 59 58 57 56 55 54 53 52 51

PS3006

|    |         |    | 1      |    | 1       |     |         |

|----|---------|----|--------|----|---------|-----|---------|

| 1  | FCLE1   | 26 | VCC3   | 51 | FCE11-  | 76  | VCC5A   |

| 2  | FALE1   | 27 | VSS    | 52 | VCC3    | 77  | GNDA    |

| 3  | FWE1-   | 28 | VSSK   | 53 | VSS     | 78  | VSS     |

| 4  | GPIO0   | 29 | FCE7-  | 54 | HCS1-   | 79  | TESTEXT |

| 5  | VCC3    | 30 | FD0    | 55 | HA2     | 80  | FCE1-   |

| 6  | VSS     | 31 | FD8    | 56 | PDIAG-  | 81  | FRDY0   |

| 7  | VSSK    | 32 | FD1    | 57 | IOIS16- | 82  | FRE0-   |

| 8  | VCCK    | 33 | FD9    | 58 | CSEL    | 83  | FCE0-   |

| 9  | HRESET- | 34 | FD2    | 59 | HIOW-   | 84  | FCE2-   |

| 10 | HD7     | 35 | FD10   | 60 | IORDY   | 85  | FCE3-   |

| 11 | HD6     | 36 | FD3    | 61 | HWE-    | 86  | FCE6-   |

| 12 | HD5     | 37 | FD11   | 62 | HD15-   | 87  | FCLE0   |

| 13 | HD4     | 38 | FD4    | 63 | HD14-   | 88  | FCE4-   |

| 14 | HD3     | 39 | FD12   | 64 | HD13-   | 89  | FALE0   |

| 15 | HD2     | 40 | FD5    | 65 | HD12-   | 90  | FCE5-   |

| 16 | HD1     | 41 | VCCK   | 66 | HD11-   | 91  | FWE0-   |

| 17 | HD0     | 42 | FD13   | 67 | HD10-   | 92  | FWP-    |

| 18 | HOE-    | 43 | FD6    | 68 | HD9-    | 93  | FRDY1   |

| 19 | DMARQ   | 44 | FD14   | 69 | HD8-    | 94  | FRDY2   |

| 20 | HIOR-   | 45 | FD7    | 70 | DASP-   | 95  | FRDY3   |

| 21 | DMACK-  | 46 | FD15   | 71 | ROMOE-  | 96  | FCE12-  |

| 22 | INTRQ   | 47 | DEVSEL | 72 | VCC3    | 97  | FCE13-  |

| 23 | HA1     | 48 | FCE8-  | 73 | VCCK    | 98  | FCE14-  |

| 24 | HA0     | 49 | FCE9-  | 74 | V18     | 99  | FCE15-  |

| 25 | HCS0-   | 50 | FCE10- | 75 | V33     | 100 | FRE1-   |

D3. PACKAGE TYPE : BGA85

TOP VIEW (Balls Face Down)

| VSS  | VSS    | HCS0#   | INTRQ | HOE#         | HD1          | NC   | HD6    | VSS     | HRESET# |

|------|--------|---------|-------|--------------|--------------|------|--------|---------|---------|

| FD0  | FD8    | FCE7#   | HA1   | HIOR#        | HD0          | HD3  | HD5    | HD7     | VCCK    |

| FD1  | FD9    | FD2     | HA0   | DMACK#       | DMARQ        | HD2  | HD4    | TESTRST | GNDA    |

| FD10 | FD3    | FD11    |       |              |              |      | WP_PD# | FWE0#   | FCE5#   |

| VSS  | VCC3IO | FD4     |       |              |              |      | FALE0  | FCE4#   | FCLE0   |

| FD12 | FD5    | FD13    |       |              |              |      | FCE6#  | FCE3#   | VSS     |

| FD6  | FD14   | FD7     | vss   |              |              |      | FCE2#  | FCE0#   | VCC3IO  |

| FD15 | NC     | CSEL    | HD15  | HD13         | HDU          | HD8  | FRE0#  | FRDY0   | FCE1#   |

| VSS  | HA2    | IOIS16# | IORDY | HD13<br>HD14 | HD11<br>HD12 | HD9  | DASP#  | TESTEXT | VCCK    |

| VSSK | HCS1#  | PDIAG#  | HIOW# | VSS          | VOC5A        | HD10 | VSS    | V33     | VI8     |

| A    | В      | С       | D     | E            | F            | G    | Н      | J       | K       |

|     |         |     |        |     |        |     | -       |

|-----|---------|-----|--------|-----|--------|-----|---------|

| A1  | VSSK    | C3  | CSEL   | F2  | HD12   | J2  | TESTEXT |

| A2  | VSS     | C4  | FD7    | F3  | HD11   | J3  | FRDY0   |

| A3  | FD15    | C5  | FD13   | F8  | DMARQ  | J4  | FCE0-   |

| A4  | FD6     | C6  | FD4    | F9  | HD0    | J5  | FCE3-   |

| A5  | FD12    | C7  | FD11   | F10 | HD1    | J6  | FCE4-   |

| A6  | VSS     | C8  | FD2    | G1  | HD10   | J7  | FWE0-   |

| A7  | FD10    | C9  | FCE7-  | G2  | HD9    | J8  | TESTRST |

| A8  | FD1     | C10 | HCS0-  | G3  | HD8    | J9  | HD7     |

| A9  | FD0     | D1  | HIOW-  | G8  | HD2    | J10 | VSS     |

| A10 | VSS     | D2  | IORDY  | G9  | HD3    | K1  | V18     |

| B1  | HCS1-   | D3  | HD15   | G10 | NC     | K2  | VCCK    |

| B2  | HA2     | D4  | VSS    | H1  | VSS    | K3  | FCE1-   |

| B3  | NC      | D8  | HA0    | H2  | DASP-  | K4  | VCC3IO  |

| B4  | FD14    | D9  | HA1    | H3  | FRE0-  | K5  | VSS     |

| B5  | FD5     | D10 | INTRQ  | H4  | FCE2-  | K6  | FCLE0   |

| B6  | VCC3IO  | E1  | VSS    | H5  | FCE6-  | K7  | FCE5-   |

| B7  | FD3     | E2  | HD14   | H6  | FALE0  | K8  | GNDA    |

| B8  | FD9     | E3  | HD13   | H7  | WP_PD- | K9  | VCCK    |

| B9  | FD8     | E8  | DMACK- | H8  | HD4    | K10 | HRESET- |

| B10 | VSS     | E9  | HIOR-  | H9  | HD5    |     |         |

| C1  | PDIAG-  | E10 | HOE-   | H10 | HD6    |     |         |

| C2  | IOIS16- | F1  | VCC5A  | J1  | V33    | ]   |         |

# E. Pin Description

| Pin Name                                                                                             | Dir. | PU/PD      | Description                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |

|------------------------------------------------------------------------------------------------------|------|------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| HA[10:0]<br>(PC Card Memory<br>Mode)<br>HA[10:0]<br>(PC Card I/O Mode)<br>HA[2:0]<br>(True IDE Mode) | I    | PD<br>300K | These address lines along with the DMACK-(REG-) signal are<br>used to select the following: The I/O port address registers within<br>the CompactFlash Storage Card or CF+ Card, the memory<br>mapped port address registers within the CompactFlash Storage<br>Card or CF+ Card, a byte in the card's information structure and<br>its configuration control and status registers.<br>This signal is the same as the PC Card Memory Mode signal.<br>In True IDE Mode, only HA[2:0] are used to select the one of<br>eight registers in the Task File, the remaining address lines<br>should be grounded by the host. |

| HD[15:0]<br>(PC Card Memory<br>Mode)                                                                 | I/O  | PD<br>300K | These lines carry the Data, Commands and Status information<br>between the host and the controller. HD[0] is the LSB of the Even<br>Byte of the Word. HD[8] is the LSB of the Odd Byte of the Word.                                                                                                                                                                                                                                                                                                                                                                                                                  |

| (PC Card I/O Mode)                                                                                   |      |            | This signal is the same as the PC Card Memory Mode signal.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |

| (True IDE Mode)                                                                                      |      |            | In True IDE Mode all Task File operations occur in byte mode on the low order bus HD[0]-HD[7] while all data transfers are 16bit using HD[0]-HD[15].                                                                                                                                                                                                                                                                                                                                                                                                                                                                 |

| HCS0-,HCS1-<br>(PC Card Memory<br>Mode)<br>(PC Card I/O Mode)                                        | I    | PU<br>300K | These input signals are used to select the card and to indicate to<br>the card whether a byte or a word operation is being performed.<br>HCS1- always accesses the odd byte of the word. HCS0-<br>accesses the even byte or the Odd byte of the word depending<br>on the A0 and HCS1<br>This signal is the same as the PC Card Memory Mode signal                                                                                                                                                                                                                                                                    |

| (True IDE Mode)                                                                                      |      |            | HCS0- is the address range select for the task file registers while<br>HCS1- is used to select the Alternate Status Register and the<br>Device Control Register. While DMACK- is asserted, HCS0- and<br>HCS1- shall be held negated and the width of the transfers shall<br>be 16 bits.                                                                                                                                                                                                                                                                                                                              |

| DMACK-<br>(PC Card Memory<br>Mode)                                                                   | I    | PU<br>300K | This signal is used during Memory Cycles to distinguish between<br>Common Memory and Register (Attribute) Memory accesses.<br>High for Common Memory, Low for Attribute Memory.                                                                                                                                                                                                                                                                                                                                                                                                                                      |

| (PC Card I/O Mode)<br>(True IDE Mode)                                                                |      |            | The signal must also be active (low) during I/O Cycles when the I/O address is on the Bus.<br>This is a DMA Acknowledge signal that is asserted by the host in response to (-)DMARQ to initiate DMA transfers.<br>In True IDE Mode, while DMA operations are not active, the card shall ignore the (-)DMACK signal, including a floating condition.<br>If DMA operation is not supported by a True IDE Mode only host, this signal should be driven high or connected to VCC by the host.                                                                                                                            |

| HOE-<br>(PC Card Memory<br>Mode)                                                                     |      | PU<br>300K | This is an Output Enable strobe generated by the host interface.<br>It is used to read data from the CompactFlash Storage Card in<br>Memory Mode and to read the CIS and configuration registers.                                                                                                                                                                                                                                                                                                                                                                                                                    |

| (PC Card I/O Mode)                                                                                   |      |            | In PC Card I/O Mode, this signal is used to read the CIS and<br>configuration registers.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             |

| (True IDE Mode)                                                                                      |      |            | To enable True IDE Mode this input should be grounded by the host.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |

| Knows What                                                                   | Too He | eo         | 1 0000                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |

|------------------------------------------------------------------------------|--------|------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| HWE-<br>(PC Card Memory<br>Mode)                                             | I      | PU<br>300K | This is a signal driven by the host and used for strobing memory<br>write data to the registers of the CompactFlash Storage Card<br>when the card is configured in the memory interface mode. It is<br>also used for writing the configuration registers.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             |

| (PC Card I/O Mode)<br>(True IDE Mode)                                        |        |            | In PC Card I/O Mode, this signal is used for writing the configuration registers.<br>In True IDE Mode this input signal is not used and should be connected to VCC by the host.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       |

| HIOR-<br>(PC Card Memory<br>Mode)<br>(PC Card I/O Mode)<br>(True IDE Mode)   | 1      | РU<br>300К | This signal is not used in this mode.<br>This is an I/O Read strobe generated by the host. This signal<br>gates I/O data onto the bus from the CompactFlash Storage Card<br>when the card is configured to use the I/O interface.<br>In True IDE Mode, while Ultra DMA mode is not active, this<br>signal has the same function as in PC Card I/O Mode.<br>In all modes when Ultra DMA mode DMA Read is active, this<br>signal is asserted by the host to indicate that the host is ready to<br>receive Ultra DMA data-in bursts. The host may<br>negate –HDMARDY to pause an Ultra DMA transfer.<br>In all modes when Ultra DMA mode DMA Write is active, this<br>signal is the data out strobe generated by the host. Both the<br>rising and falling edge of HSTROBE cause data to be latched by<br>the device. The host may stop generating HSTROBE edges to<br>pause an Ultra DMA data-out burst. |

| HIOW-<br>(PC Card Memory<br>Mode)<br>(PC Card I/O Mode)<br>(True IDE Mode)   | 1      | РU<br>300К | This signal is not used in this mode.<br>The I/O Write strobe pulse is used to clock I/O data on the Card<br>Data bus into the CompactFlash Storage Card controller<br>registers when the CompactFlash Storage Card is configured to<br>use the I/O interface.<br>The clocking will occur on the negative to positive edge of the<br>signal (trailing edge).<br>In True IDE Mode, while Ultra DMA mode protocol is not active,<br>this signal has the same function as in PC Card I/O Mode.<br>When Ultra DMA mode protocol is supported, this signal must be<br>negated before entering Ultra DMA mode protocol.<br>In All Modes, while Ultra DMA mode protocol is active, the<br>assertion of this signal causes the termination of the Ultra DMA<br>data burst.                                                                                                                                    |

| HRESET-<br>(PC Card Memory<br>Mode)<br>(PC Card I/O Mode)<br>(True IDE Mode) | 1      | PU<br>300K | The CompactFlash Storage Card or CF+ Card is Reset when the<br>RESET pin is high with the following important exception:<br>The host may leave the RESET pin open or keep it continually<br>high from the application of power without causing a continuous<br>Reset of the card. Under either of these conditions, the card shall<br>emerge from power-up having completed an initial Reset.<br>The CompactFlash Storage Card or CF+ Card is also Reset<br>when the Soft Reset bit in the Card Configuration Option<br>Register is set.<br>This signal is the same as the PC Card Memory Mode signal.<br>In the True IDE Mode this input pin is the active low hardware<br>reset from the host.                                                                                                                                                                                                      |

| DMARQ<br>(PC Card Memory<br>Mode)                                            | 0      |            | This signal is not used in this mode.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 |

| Knows What         | You Ne | ed   | F 33000                                                               |

|--------------------|--------|------|-----------------------------------------------------------------------|

| (PC Card I/O Mode) |        |      | The Input Acknowledge signal is asserted by the CompactFlash          |

|                    |        |      | Storage Card when the card is selected and responding to an I/O       |

|                    |        |      | read cycle at the address that is on the address bus. This signal     |

|                    |        |      | is used by the host to control the enable of any input data buffers   |

|                    |        |      | between the CompactFlash Storage Card and the CPU                     |

| (True IDE Mode)    |        |      | This signal is a DMA Request that is used for DMA data transfers      |

| (                  |        |      | between host and device. It shall be asserted by the device when      |

|                    |        |      | it is ready to transfer data to or from the host. For Multiword DMA   |

|                    |        |      | transfers, the direction of data transfer is controlled by HIOR-      |

|                    |        |      | and HIOW This signal is used in a handshake manner with               |

|                    |        |      | DMACK-, i.e., the device shall wait until the host asserts            |

|                    |        |      | DMACK- before negating DMARQ, and re-asserting DMARQ if               |

|                    |        |      | there is more data to transfer.                                       |

| HINTRQ             | 0      |      | In Memory Mode this signal is set high when the CompactFlash          |

| (PC Card Memory    | 0      |      | Storage Card is ready to accept a new data transfer operation         |

| Mode)              |        |      | and held low when the card is busy. The Host memory card              |

| inicae)            |        |      | socket must provide a pull-up resistor.                               |

|                    |        |      | At power up and at Reset the READY signal is held low (busy)          |

|                    |        |      | until the CompactFlash Storage Card has completed its power up        |

|                    |        |      | or reset function. No access of any type should be made to the        |

|                    |        |      | CompactFlash Storage Card during this time.                           |

|                    |        |      | Note, however, that when a card is powered up and used with           |

|                    |        |      | RESET continuously disconnected or asserted, the Reset                |

|                    |        |      | function of the RESET pin is disabled. Consequently, the              |

|                    |        |      | continuous assertion of RESET from the application of power           |

|                    |        |      | shall not cause the READY signal to remain continuously in the        |

|                    |        |      | busy state.                                                           |

| (PC Card I/O Mode) |        |      | After the CompactFlash Storage Card has been configured for           |

| (                  |        |      | I/O operation, this signal is used as Interrupt Request. This line is |

|                    |        |      | strobed low to generate a pulse mode interrupt or held low for a      |

|                    |        |      | level mode interrupt.                                                 |

| (True IDE Mode)    |        |      | In True IDE Mode signal is the active high Interrupt Request to       |

| (                  |        |      | the host.                                                             |

| IOIS16-            | 0      | PU   | The CompactFlash Storage Card does not have a write protect           |

| (PC Card Memory    | 0      | FU   | switch. This signal is held low after the completion of the reset     |

| Mode)              |        | 300K | initialization sequence.                                              |

| (PC Card I/O Mode) |        |      | When the CompactFlash Storage Card is configured for I/O              |

|                    |        |      | Operation IOIS16- is used for the -I/O Selected is 16 Bit Port        |

|                    |        |      | function. A Low signal indicates that a 16 bit or odd byte only       |

|                    |        |      | operation can be performed at the addressed port.                     |

| (True IDE Mode)    |        |      | In True IDE Mode this output signal is asserted low when this         |

| (                  |        |      | device is expecting a word data transfer cycle.                       |

| PDIAG-             | I/O    | PU   | This signal is asserted high (BVD1 is not supported).                 |

| (PC Card Memory    | 1/0    | PU   |                                                                       |

| Mode)              |        | 300K |                                                                       |

| (PC Card I/O Mode) |        |      | This signal is asserted low to alert the host to changes in the       |

|                    |        |      | READY and Write Protect states, while the I/O interface is            |

|                    |        |      | configured. Its use is controlled by the Card Config and Status       |

|                    |        |      | Register.                                                             |

| (True IDE Mode)    |        |      | This input/ output is the Pass Diagnostic signal in the Master/       |

|                    |        |      | Slave handshake protocol                                              |

| DASP-              | I/O    | PU   | This signal is asserted high (BVD2 is not supported).                 |

| (PC Card Memory    |        | _    |                                                                       |

| Mode)              |        | 300K |                                                                       |

| (PC Card I/O Mode) |        |      | This signal is held negated.                                          |

| (True IDE Mode)    |        |      | This input/ output is the Disk Active/Slave Present signal in the     |

| (                  |        |      | Disk Master/Slave handshake protocol.                                 |

|                    |        | 1    |                                                                       |

| CSEL<br>(PC Card Memory<br>Mode)      | I       | PU<br>300K | This signal is not used for this mode, but should be connected by the host to PC Card A25 or grounded by the host.                                                                                                                                                                                                                                |

|---------------------------------------|---------|------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| (PC Card I/O Mode)<br>(True IDE Mode) |         |            | This signal is not used for this mode, but should be connected by<br>the host to PC Card A25 or grounded by the host.<br>This internally pulled up signal is used to configure this device as<br>a Master or a Slave when configured in the True IDE Mode.                                                                                        |

|                                       |         |            | When this pin is grounded, this device is configured as a Master.<br>When the pin is open, this device is configured as a Slave.                                                                                                                                                                                                                  |

| IORDY<br>(PC Card Memory<br>Mode)     | 0       |            | This signal is driven low by the CompactFlash Storage Card to signal the host to delay completion of a memory or I/O cycle that is in progress                                                                                                                                                                                                    |

| (PC Card I/O Mode)                    |         |            | This signal is the same as the PC Card Memory Mode signal                                                                                                                                                                                                                                                                                         |

| (True IDE Mode)                       |         |            | In True IDE Mode, except in Ultra DMA modes, this output signal<br>may be used as IORDY.<br>When Ultra DMA mode DMA Write is active, this signal is<br>asserted by the device during a data burst to indicate that the<br>device is ready to receive Ultra DMA data out bursts. The device<br>may negate -DDMARDY to pause an Ultra DMA transfer. |

|                                       |         |            | When Ultra DMA mode DMA Read is active, this signal is the data in strobe generated by the device. Both the rising and falling edge of DSTROBE cause data to be latched by the host. The device may stop generating DSTROBE edges to pause an Ultra DMA data in burst.                                                                            |

| FCE-[15:0]                            | 0       | PU 75K     | Flash Chip Enable, Low active.                                                                                                                                                                                                                                                                                                                    |

| FD[15:0]                              | I/O     | PD 75K     | Flash Data Bus                                                                                                                                                                                                                                                                                                                                    |

| FALE[1:0]                             | 0       |            | Flash Address Latch Enable, High active.                                                                                                                                                                                                                                                                                                          |

| FCLE[1:0]                             | 0       |            | Flash Command Latch Enable, High active.                                                                                                                                                                                                                                                                                                          |

| FRE[1:0]                              | 0       |            | Flash Read Control signal, Low active.                                                                                                                                                                                                                                                                                                            |

| FWE[1:0]                              | 0       |            | Flash Write Control signal, Low active.                                                                                                                                                                                                                                                                                                           |

| FWP-                                  | I/O     |            | Flash Write Protect Control signal, Low active.                                                                                                                                                                                                                                                                                                   |

| FRDY0, FRDY1                          |         | PU 75K     | Flash Ready/Busy signal.                                                                                                                                                                                                                                                                                                                          |

| Test[2:0]                             | I/O     | PD 75K     | Test Mode Signal.                                                                                                                                                                                                                                                                                                                                 |

| TestExt                               | I/O     |            | Test Mode Signal.                                                                                                                                                                                                                                                                                                                                 |

| DEVSel                                |         |            | Select flash/MMC interface                                                                                                                                                                                                                                                                                                                        |

| GPIO0<br>GPIO2<br>GPIO3               | I/O     | PU 75K     | General purpose input/output pins                                                                                                                                                                                                                                                                                                                 |

| VCC5A                                 | VC<br>C |            | 5V/3.3V input                                                                                                                                                                                                                                                                                                                                     |

| V18                                   | VC<br>C |            | 1.8V output                                                                                                                                                                                                                                                                                                                                       |

| V33                                   | VC<br>C |            | 3.3V output                                                                                                                                                                                                                                                                                                                                       |

| VCC3                                  | VC<br>C |            | 3.3V in                                                                                                                                                                                                                                                                                                                                           |

| VCCK                                  | VC<br>C |            | 1.8V in                                                                                                                                                                                                                                                                                                                                           |

| GND                                   | GN<br>D |            |                                                                                                                                                                                                                                                                                                                                                   |

| GNDA                                  | GN<br>D |            |                                                                                                                                                                                                                                                                                                                                                   |

\*Note :

## 1. FCE[15:8] and ext ROM Data[7:0] share the same pins

2. All I/O Pin are push pull type.

# F. System Power Consumption

| Symbol | Parameter                 | Condition | MIN | TYP | MAX | Unit |

|--------|---------------------------|-----------|-----|-----|-----|------|

| lccr   | Read current              | 5V        |     | 75  |     | mA   |

| lccw   | Write current             | 5V        |     | 75  |     | mA   |

| lpd    | Power down current        | 5V        |     |     |     | mA   |

| lccr   | Read current              | 3.3V      |     | 55  |     | mA   |

| lccw   | Write current             | 3.3V      |     | 55  |     | mA   |

| lpd    | Power down current        | 3.3V      |     |     |     | mA   |

| Ireg   | Regulator leakage current | 3.3V      |     |     |     | mA   |

# **G. Electrical Specifications**

### Absolute Maximum Rating

| ltem | Symbol              | Parameter             | MIN           | MAX                  | Unit | Remark             |

|------|---------------------|-----------------------|---------------|----------------------|------|--------------------|

| 1    | $V_{DD}$ - $V_{SS}$ | DC Power Supply       | -0.3          | +5.5                 | V    |                    |

| 2    | V <sub>IN</sub>     | Input Voltage         | $V_{SS}$ -0.3 | V <sub>DD</sub> +0.3 | V    |                    |

| 3    | Та                  | Operating Temperature | 0             | +70                  | °C   | Commercial version |

| 4    | Tst                 | Storage Temperature   | 0             | +85                  | °C   | Commercial version |

| 5    | Та                  | Operating Temperature | -40           | +85                  | °C   | Industry version   |

| 6    | Tst                 | Storage Temperature   | -40           | +100                 | °C   | Industry version   |

| Parameter       | Symbol          | Min | Тур | ΜΑΧ  | Unit |

|-----------------|-----------------|-----|-----|------|------|

| Operating       | Ta              | -40 | +25 | +125 | °C   |

| Temperature     |                 |     |     |      |      |

| V <sub>DD</sub> | V <sub>DD</sub> | 3.0 | 3.3 | 3.6  | V    |

| Voltage         |                 | 4.5 | 5.0 | 5.5  | V    |

### Schmit Trigger Pin:

I = Input O = Output

| Pin Name                    | Pin Number | IOL<br>(mA) | Dir |                               |

|-----------------------------|------------|-------------|-----|-------------------------------|

| HOE-, HWE-,<br>HIOR-, HIOW- | 4          | 12          | I   | TTL Level Pull-up 300K(SCHMT) |

| REG-, CE1-, CE2-            | 3          | 12          | I   | TTL Level Pull-up 300K(SCHMT) |

| HRST                        | 1          | 12          | I   | TTL Level(SCHMT)              |

# H. DC Characters

### 1. DC characteristics of 3.3V I/O Cells

| Symbol | Parameter                  | Conditions       | MIN | TYP | MAX | Unit |

|--------|----------------------------|------------------|-----|-----|-----|------|

| VCC3I  | Power Supply               | 3.3V I/O         | 3.0 | 3.3 | 3.6 | V    |

| VCC3O  | Power Supply               |                  | 3.0 | 3.3 | 3.6 | V    |

| Temp   | Junction Temperature       |                  | -40 | 25  | 125 | °C   |

| Vt-    | Schmitt Trigger Negative   |                  |     | 1.1 |     | V    |

|        | Going threshold voltage    | CMOS             |     |     |     |      |

| Vt+    | Schmitt Trigger Positive   |                  |     | 1.6 |     | V    |

|        | Going threshold voltage    |                  |     |     |     |      |

| Vol    | Output Low voltage         | lol  = 4 ~ 32 mA |     |     | 0.4 | V    |

| Voh    | Output High voltage        | loh  = 4 ~ 32 mA | 2.4 |     |     | V    |

| Rpu    | Input Pull-Up Resistance   | PU=high,         | 40  | 75  | 190 | KΩ   |

|        |                            | PD=low           |     |     |     |      |

| Rpd    | Input Pull-Down Resistance | PU=high,         | 40  | 75  | 190 | KΩ   |

|        |                            | PD=low           |     |     |     |      |

| lin    | Input Leakage Current      | Vin = VCC3I or 0 | -10 | ±1  | 10  | μA   |

| loz    | Tri-state Output Leakage   |                  | -10 | ±1  | 10  | μA   |

|        | Current                    |                  |     |     |     |      |

### 2. DC characteristics of 5V tolerance I/O Cells

| Symbol | Parameter                  | Conditions       | MIN | TYP  | MAX | Unit |

|--------|----------------------------|------------------|-----|------|-----|------|

| VCC3I  | Power Supply               | 3.3V I/O         | 3.0 | 3.3  | 3.6 | V    |

| VCC3O  | Power Supply               |                  | 3.0 | 3.3  | 3.6 | V    |

| Temp   | Junction Temperature       |                  | -40 | 25   | 125 | °C   |

| Vt-    | Schmitt Trigger Negative   |                  |     | 0.85 |     | V    |

|        | Going threshold voltage    | TTL              |     |      |     |      |

| Vt+    | Schmitt Trigger Positive   | (3.3V)           |     | 1.25 |     | V    |

|        | Going threshold voltage    |                  |     |      |     |      |

| Vt-    | Schmitt Trigger Negative   |                  |     | 1.05 |     | V    |

|        | Going threshold voltage    | TTL              |     |      |     |      |

| Vt+    | Schmitt Trigger Positive   | (5V)             |     | 1.75 |     | V    |

|        | Going threshold voltage    |                  |     |      |     |      |

| Vol    | Output Low voltage         | lol  = 4 ~ 32 mA |     |      | 0.4 | V    |

| Voh    | Output High voltage        | loh  = 4 ~ 32 mA | 2.4 |      |     | V    |

| Rpu    | Input Pull-Up Resistance   | PU=high,         | 200 | 300  | 450 | KΩ   |

|        |                            | PD=low           |     |      |     |      |

| Rpd    | Input Pull-Down Resistance | PU=high,         | 200 | 300  | 450 | KΩ   |

|        |                            | PD=low           |     |      |     |      |

| lin    | Input Leakage Current      | Vin = VCC3I or 0 | -10 | ±1   | 10  | μA   |

| loz    | Tri-state Output Leakage   |                  | -10 | ±1   | 10  | μA   |

|        | Current                    |                  |     |      |     |      |

# I. AC Characters

### **I1. PCMCIA Interface**

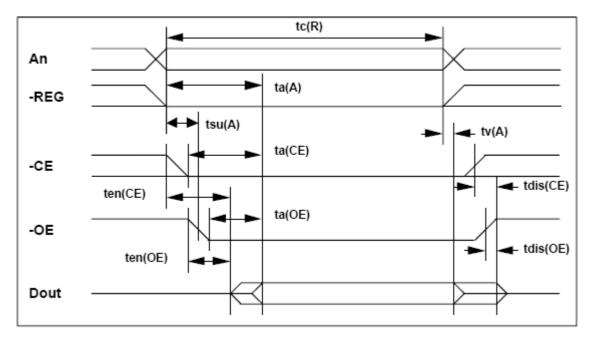

[Attribute Memory Read Timing]

| Speed Version                  |          |             | 300     | ns      |

|--------------------------------|----------|-------------|---------|---------|

| Item                           | Symbol   | IEEE Symbol | Min ns. | Max ns. |

| Read Cycle Time                | tc(R)    | tAVAV       | 300     |         |

| Address Access Time            | ta(A)    | tAVQV       |         | 300     |

| Card Enable Access Time        | ta(CE)   | tELQV       |         | 300     |

| Output Enable Access Time      | ta(OE)   | tGLQV       |         | 150     |

| Output Disable Time from CE    | tdis(CE) | tEHQZ       |         | 100     |

| Output Disable Time from OE    | tdis(OE) | tGHQZ       |         | 100     |

| Address Setup Time             | tsu (A)  | tAVGL       | 30      |         |

| Output Enable Time from CE     | ten(CE)  | tELQNZ      | 5       |         |

| Output Enable Time from OE     | ten(OE)  | tGLQNZ      | 5       |         |

| Data Valid from Address Change | tv(A)    | tAXQX       | 0       |         |

Note: All times are in nanoseconds. Dout signifies data provided by the CompactFlash Storage Card or CF+ Card to the system. The -CE signal or both the -OE signal and the -WE signal shall be de-asserted between consecutive cycle operations.

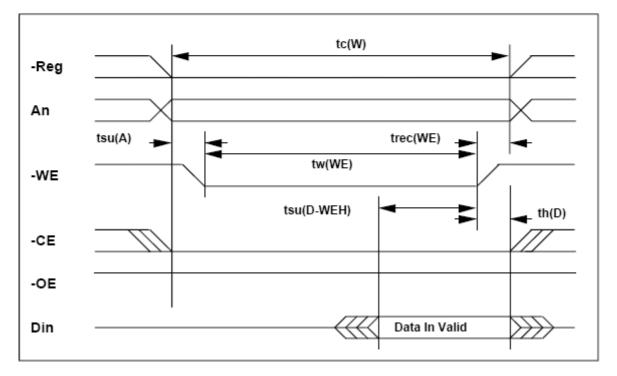

| Speed Version          |            |             | 250    | ns     |

|------------------------|------------|-------------|--------|--------|

| Item                   | Symbol     | IEEE Symbol | Min ns | Max ns |

| Write Cycle Time       | tc(W)      | tavav       | 250    |        |

| Write Pulse Width      | tw(WE)     | tWLWH       | 150    |        |

| Address Setup Time     | tsu(A)     | tA∨WL       | 30     |        |

| Write Recovery Time    | trec(WE)   | tWMAX       | 30     |        |

| Data Setup Time for WE | tsu(D-WEH) | tD∨WH       | 80     |        |

| Data Hold Time         | th(D)      | tWMDX       | 30     |        |

Note: All times are in nanoseconds. Din signifies data provided by the system to the CompactFlash Storage Card or CF+ Card.

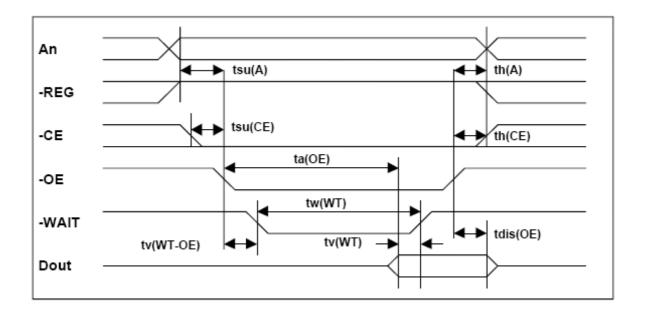

|                                 | Cycle     | Time Mode:     | 250        | ) ns                        | 120        | ) ns                        | 100        | ns                          | 80         | ns              |

|---------------------------------|-----------|----------------|------------|-----------------------------|------------|-----------------------------|------------|-----------------------------|------------|-----------------|

| ltem                            | Symbol    | IEEE<br>Symbol | Min<br>ns. | Max<br>ns.                  | Min<br>ns. | Max<br>ns.                  | Min<br>ns. | Max<br>ns.                  | Min<br>ns. | Max<br>ns.      |

| Output Enable<br>Access Time    | ta(OE)    | tGLQV          |            | 125                         |            | 60                          |            | 50                          |            | 45              |

| Output Disable<br>Time from OE  | tdis(OE)  | tGHQZ          |            | 100                         |            | 60                          |            | 50                          |            | 45              |

| Address Setup<br>Time           | tsu(A)    | tAVGL          | 30         |                             | 15         |                             | 10         |                             | 10         |                 |

| Address Hold<br>Time            | th(A)     | tGHAX          | 20         |                             | 15         |                             | 15         |                             | 10         |                 |

| CE Setup<br>before OE           | tsu(CE)   | tELGL          | 0          |                             | 0          |                             | 0          |                             | 0          |                 |

| CE Hold<br>following OE         | th(CE)    | tGHEH          | 20         |                             | 15         |                             | 15         |                             | 10         |                 |

| Wait Delay<br>Falling from OE   | tv(WT-OE) | tGLWT∨         |            | 35                          |            | 35                          |            | 35                          |            | na <sup>1</sup> |

| Data Setup for<br>Wait Release  | tv(WT)    | tQVWTH         |            | 0                           |            | 0                           |            | 0                           |            | na1             |

| Wait Width<br>Time <sup>2</sup> | tw(WT)    | tWTLWTH        |            | 350<br>(3000<br>for<br>CF+) |            | 350<br>(3000<br>for<br>CF+) |            | 350<br>(3000<br>for<br>CF+) |            | na <sup>1</sup> |

Notes: 1) -WAIT is not supported in this mode.

2) The maximum load on -WAIT is 1 LSTTL with 50 pF (40pF below 120nsec Cycle Time) total load. All times are in nanoseconds. Dout signifies data provided by the CompactFlash Storage Card or CF+ Card to the system. The -WAIT signal may be ignored if the -OE cycle to cycle time is greater than the Wait Width time. The Max Wait Width time can be determined from the Card Information Structure. The Wait Width time meets the PCMCIA specification of 12µs but is intentionally less in this specification.

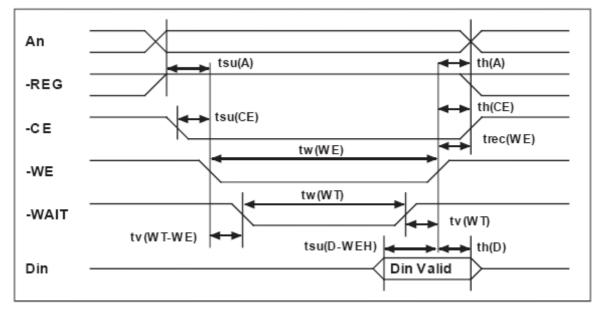

#### [Common Memory Write Timing]

|                                 | Cycle          | Time Mode:     | 250        | ) ns                        | 120        | ns                          | 100        | ns                          | 80         | ns              |

|---------------------------------|----------------|----------------|------------|-----------------------------|------------|-----------------------------|------------|-----------------------------|------------|-----------------|

| Item                            | Symbol         | IEEE<br>Symbol | Min<br>ns. | Max<br>ns.                  | Min<br>ns. | Max<br>ns.                  | Min<br>ns. | Max<br>ns.                  | Min<br>ns. | Max<br>ns.      |

| Data Setup<br>before WE         | tsu<br>(D-WEH) | tD∨WH          | 80         |                             | 50         |                             | 40         |                             | 30         |                 |

| Data Hold<br>following WE       | th(D)          | tWMDX          | 30         |                             | 15         |                             | 10         |                             | 10         |                 |

| WE Pulse Width                  | tw(WE)         | tWLWH          | 150        |                             | 70         |                             | 60         |                             | 55         |                 |

| Address Setup<br>Time           | tsu(A)         | tA∨WL          | 30         |                             | 15         |                             | 10         |                             | 10         |                 |

| CE Setup<br>before WE           | tsu(CE)        | tELWL          | 0          |                             | 0          |                             | 0          |                             | 0          |                 |

| Write Recovery<br>Time          | trec(WE)       | tWMAX          | 30         |                             | 15         |                             | 15         |                             | 15         |                 |

| Address Hold<br>Time            | th(A)          | tGHAX          | 20         |                             | 15         |                             | 15         |                             | 15         |                 |

| CE Hold<br>following WE         | th(CE)         | tGHEH          | 20         |                             | 15         |                             | 15         |                             | 10         |                 |

| Wait Delay<br>Falling from WE   | tv<br>(WT-WE)  | tWLWT∨         |            | 35                          |            | 35                          |            | 35                          |            | na¹             |

| WE High from<br>Wait Release    | tv(WT)         | tWTHWH         | 0          |                             | 0          |                             | 0          |                             | na¹        |                 |

| Wait Width<br>Time <sup>2</sup> | tw (WT)        | tWTLWTH        |            | 350<br>(3000<br>for<br>CF+) |            | 350<br>(3000<br>for<br>CF+) |            | 350<br>(3000<br>for<br>CF+) |            | na <sup>1</sup> |

Notes: 1) -WAIT is not supported in this mode.

2) The maximum load on -WAIT is 1 LSTTL with 50 pF (40pF below 120nsec Cycle Time) total load. All times are in nanoseconds. Din signifies data provided by the system to the CompactFlash Storage Card. The -WAIT signal may be ignored if the -WE cycle to cycle time is greater than the Wait Width time. The Max Wait Width time can be determined from the Card Information Structure. The Wait Width time meets the PCMCIA specification of 12µs but is intentionally less in this specification.

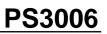

### [I/O Read Timing]

|                                                   | Cycle               | Time Mode:     | 255        | ö ns                        | 120        | ) ns                        | 100        | ) ns                        | 80         | ns         |

|---------------------------------------------------|---------------------|----------------|------------|-----------------------------|------------|-----------------------------|------------|-----------------------------|------------|------------|

| Item                                              | Symbol              | IEEE<br>Symbol | Min<br>ns. | Max<br>ns.                  | Min<br>ns. | Max<br>ns.                  | Min<br>ns. | Max<br>ns.                  | Min<br>ns. | Max<br>ns. |

| Data Delay after<br>IORD                          | td(IORD)            | tIGLQV         |            | 100                         |            | 50                          |            | 50                          |            | 45         |

| Data Hold following<br>IORD                       | th(IORD)            | tIGHQX         | 0          |                             | 5          |                             | 5          |                             | 5          |            |

| IORD Width Time                                   | tw(IORD)            | tIGLIGH        | 165        |                             | 70         |                             | 65         |                             | 55         |            |

| Address Setup<br>before IORD                      | tsuA(IORD)          | tAVIGL         | 70         |                             | 25         |                             | 25         |                             | 15         |            |

| Address Hold<br>following IORD                    | thA(IORD)           | tIGHAX         | 20         |                             | 10         |                             | 10         |                             | 10         |            |

| CE Setup before<br>IORD                           | tsuCE(IORD)         | tELIGL         | 5          |                             | 5          |                             | 5          |                             | 5          |            |

| CE Hold following<br>IORD                         | thCE(IORD)          | tIGHEH         | 20         |                             | 10         |                             | 10         |                             | 10         |            |

| REG Setup before<br>IORD                          | tsuREG<br>(IORD)    | tRGLIGL        | 5          |                             | 5          |                             | 5          |                             | 5          |            |

| REG Hold following<br>IORD                        | thREG<br>(IORD)     | tIGHRGH        | 0          |                             | 0          |                             | 0          |                             | 0          |            |

| INPACK Delay<br>Falling from IORD <sup>3</sup>    | tdfINPACK<br>(IORD) | tiglial        | 0          | 45                          | 0          | na¹                         | 0          | na¹                         | 0          | na¹        |

| INPACK Delay<br>Rising from IORD <sup>3</sup>     | tdrINPACK<br>(IORD) | tighiah        |            | 45                          |            | na¹                         |            | na¹                         |            | na¹        |

| IOIS16 Delay Falling<br>from Address <sup>3</sup> | tdflOIS16<br>(ADR)  | tAVISL         |            | 35                          |            | na¹                         |            | na¹                         |            | na¹        |

| IOIS16 Delay Rising<br>from Address <sup>3</sup>  | tdrIOIS16<br>(ADR)  | tAVISH         |            | 35                          |            | na¹                         |            | na¹                         |            | na¹        |

| Wait Delay Falling<br>from IORD <sup>3</sup>      | tdWT(IORD)          | tIGLWTL        |            | 35                          |            | 35                          |            | 35                          |            | na²        |

| Data Delay from<br>Wait Rising <sup>3</sup>       | td(WT)              | tWTHQV         |            | 0                           |            | 0                           |            | 0                           |            | na²        |

| Wait Width Time <sup>3</sup>                      | tw(WT)              | tWTLWTH        |            | 350<br>(3000<br>for<br>CF+) |            | 350<br>(3000<br>for<br>CF+) |            | 350<br>(3000<br>for<br>CF+) |            | na²        |

Notes:1) -IOIS16 and -INPACK are not supported in this mode.

2) -WAIT is not supported in this mode.

3) Maximum load on -WAIT, -INPACK and -IOIS16 is 1 LSTTL with 50 pF (40pF below 120nsec Cycle Time) total load. All times are in nanoseconds. Minimum time from -WAIT high to -IORD high is 0 nsec, but minimum -IORD width shall still be met. Dout signifies data provided by the CompactFlash Storage Card or CF+ Card to the system. Wait Width time meets PCMCIA specification of 12µs but is intentionally less in this spec.

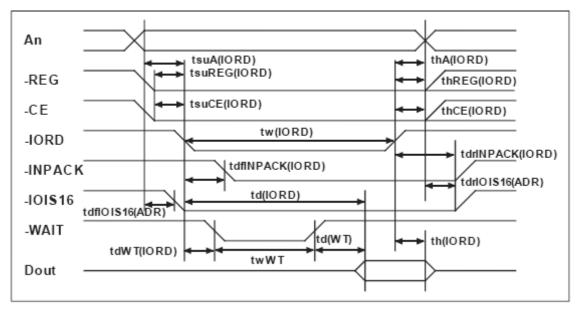

| [I/O | Write | Timing] |

|------|-------|---------|

|------|-------|---------|

|                                                   | Cycle              | Time Mode:     | 255        | ns                          | 120        | ) ns                                | 100        | ) ns                        | 80         | ns              |

|---------------------------------------------------|--------------------|----------------|------------|-----------------------------|------------|-------------------------------------|------------|-----------------------------|------------|-----------------|

| Item                                              | Symbol             | IEEE<br>Symbol | Min<br>ns. | Max<br>ns.                  | Min<br>ns. | Max<br>ns.                          | Min<br>ns. | Max<br>ns.                  | Min<br>ns. | Max<br>ns.      |

| Data Setup before<br>IOWR                         | tsu(IOWR)          | tD∨IWH         | 60         |                             | 20         |                                     | 20         |                             | 15         |                 |

| Data Hold following<br>IOWR                       | th(IOWR)           | tIWHDX         | 30         |                             | 10         |                                     | 5          |                             | 5          |                 |

| IOWR Width Time                                   | tw(IOWR)           | tIWLIWH        | 165        |                             | 70         |                                     | 65         |                             | 55         |                 |

| Address Setup<br>before IOWR                      | tsuA(IOWR)         | taviwl         | 70         |                             | 25         |                                     | 25         |                             | 15         |                 |

| Address Hold<br>following IOWR                    | thA(IOWR)          | tIWHAX         | 20         |                             | 20         |                                     | 10         |                             | 10         |                 |

| CE Setup before<br>IOWR                           | tsuCE<br>(IOWR)    | tELIWL         | 5          |                             | 5          |                                     | 5          |                             | 5          |                 |

| CE Hold following<br>IOWR                         | thCE<br>(IOWR)     | tIWHEH         | 20         |                             | 20         |                                     | 10         |                             | 10         |                 |

| REG Setup before<br>IOWR                          | tsuREG<br>(IOWR)   | tRGLIWL        | 5          |                             | 5          |                                     | 5          |                             | 5          |                 |

| REG Hold following<br>IOWR                        | thREG<br>(IOWR)    | tiWHRGH        | 0          |                             | 0          |                                     | 0          |                             | 0          |                 |

| IOIS16 Delay Falling<br>from Address <sup>3</sup> | tdflOIS16<br>(ADR) | tAVISL         |            | 35                          |            | na¹                                 |            | na¹                         |            | na <sup>1</sup> |

| IOIS16 Delay Rising<br>from Address <sup>3</sup>  | tdrIOIS16<br>(ADR) | tAVISH         |            | 35                          |            | na¹                                 |            | na¹                         |            | na <sup>1</sup> |

| Wait Delay Falling<br>from IOWR <sup>3</sup>      | tdWT(IOWR)         | tIWLWTL        |            | 35                          |            | 35                                  |            | 35                          |            | na²             |

| IOWR high from<br>Wait high <sup>3</sup>          | tdrIOWR<br>(WT)    | tWTJIWH        | 0          |                             | 0          |                                     | 0          |                             | na²        |                 |

| Wait Width Time <sup>3</sup>                      | tw(WT)             | tWTLWTH        |            | 350<br>(3000<br>for<br>CF+) |            | 350<br>(3000<br>for<br><i>CF</i> +) |            | 350<br>(3000<br>for<br>CF+) |            | na²             |

Notes: 1) -IOIS16 and -INPACK are not supported in this mode.

2) -WAIT is not supported in this mode.

3) The maximum load on -WAIT, -INPACK, and -IOIS16 is 1 LSTTL with 50 pF (40pF below 120nsec Cycle Time) total load. All times are in nanoseconds. Minimum time from -WAIT high to -IOWR high is 0 nsec, but minimum -IOWR width shall still be met. Din signifies data provided by the system to the CompactFlash Storage Card or CF+ Card. The Wait Width time meets the PCMCIA specification of 12 μs but is intentionally less in this specification.

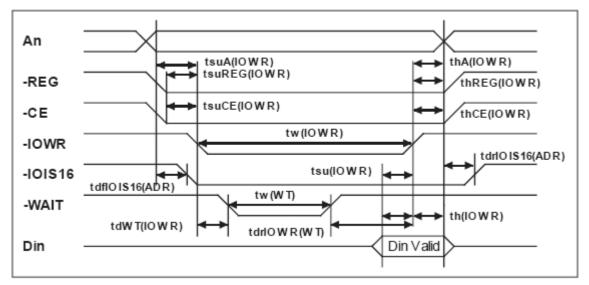

### I2. IDE Interface Timing

[PIO Mode ]

|     | ltem                                                                            | Mode<br>0 | Mode<br>1 | Mode<br>2 | Mode<br>3 | Mode<br>4 | Mode<br>5 | Mode<br>6 | Note |

|-----|---------------------------------------------------------------------------------|-----------|-----------|-----------|-----------|-----------|-----------|-----------|------|

| t0  | Cycle time (min)                                                                | 600       | 383       | 240       | 180       | 120       | 100       | 80        | 1    |

| t1  | Address Valid to -<br>IORD/-IOWR setup<br>(min)                                 | 70        | 50        | 30        | 30        | 25        | 15        | 10        |      |

| t2  | -IORD/-IOWR (min)                                                               | 165       | 125       | 100       | 80        | 70        | 65        | 55        | 1    |

| t2  | -IORD/-IOWR (min)<br>Register (8 bit)                                           | 290       | 290       | 290       | 80        | 70        | 65        | 55        | 1    |

| t2i | -IORD/-IOWR<br>recovery time (min)                                              | -         | -         | -         | 70        | 25        | 25        | 20        | 1    |

| t3  | -IOWR data setup<br>(min)                                                       | 60        | 45        | 30        | 30        | 20        | 20        | 15        |      |

| t4  | -IOWR data hold<br>(min)                                                        | 30        | 20        | 15        | 10        | 10        | 5         | 5         |      |

| t5  | -IORD data setup<br>(min)                                                       | 50        | 35        | 20        | 20        | 20        | 15        | 10        |      |

| t6  | -IORD data hold<br>(min)                                                        | 5         | 5         | 5         | 5         | 5         | 5         | 5         |      |

| t6Z | -IORD data tristate<br>(max)                                                    | 30        | 30        | 30        | 30        | 30        | 20        | 20        | 2    |

| t7  | Address valid to -<br>IOCS16 assertion<br>(max)                                 | 90        | 50        | 40        | n/a       | n/a       | n/a       | n/a       | 4    |

| t8  | Address valid to -<br>IOCS16 released<br>(max)                                  | 60        | 45        | 30        | n/a       | n/a       | n/a       | n/a       | 4    |

| t9  | -IORD/-IOWR to<br>address valid hold                                            | 20        | 15        | 10        | 10        | 10        | 10        | 10        |      |

| tRD | Read Data Valid to<br>IORDY active (min),<br>if IORDY initially low<br>after tA | 0         | 0         | 0         | 0         | 0         | 0         | 0         |      |

| tA  | IORDY Setup time                                                                | 35        | 35        | 35        | 35        | 35        | na⁵       | na⁵       | 3    |

| tΒ  | IORDY Pulse Width<br>(max)                                                      | 1250      | 1250      | 1250      | 1250      | 1250      | na⁵       | na⁵       |      |

| tC  | IORDY assertion to<br>release (max)                                             | 5         | 5         | 5         | 5         | 5         | na⁵       | na⁵       |      |

Notes: All timings are in nanoseconds. The maximum load on -IOCS16 is 1 LSTTL with a 50 pF (40pF below 120nsec Cycle Time) total load. All times are in nanoseconds. Minimum time from -IORDY high to -IORD high is 0 nsec, but minimum -IORD width shall still be met.

1) t0 is the minimum total cycle time, t2 is the minimum command active time, and t2i is the minimum command recovery time or command inactive time. The actual cycle time equals the sum of the actual command active time and the actual command inactive time. The three timing requirements of t0, t2, and t2i shall be met. The minimum total cycle time requirement is greater than the sum of t2 and t2i. This means a host implementation can lengthen either or both t2 or t2i to ensure that t0 is equal to or greater than the value reported in the device's identify device data. A CompactFlash Storage Card implementation shall support any legal host implementation.

This parameter specifies the time from the negation edge of -IORD to the time that the data bus is no longer driven by the CompactFlash Storage Card (tri-state).

3) The delay from the activation of -IORD or -IOWR until the state of IORDY is first sampled. If IORDY is inactive then the host shall wait until IORDY is active before the PIO cycle can be completed. If the CompactFlash Storage Card is not driving IORDY negated at tA after the activation of -IORD or -IOWR, then t5 shall be met and tRD is not applicable. If the CompactFlash Storage Card is driving IORDY negated at the time tA after the activation of -IORD or -IOWR, then tRD shall be met and t5 is not applicable.

4) t7 and t8 apply only to modes 0, 1 and 2. For other modes, this signal is not valid.

5) IORDY is not supported in this mode.

Notes:

Device address consists of -CS0, -CS1, and A[02::00]

(2) Data consists of D[15::00] (16-bit) or D[07::00] (8 bit)

(3) -IOCS16 is shown for PIO modes 0, 1 and 2. For other modes, this signal is ignored.

(4) The negation of IORDY by the device is used to extend the PIO cycle. The determination of whether the cycle is to be extended is made by the host after tA from the assertion of -IORD or -IOWR. The assertion and negation of IORDY is described in the following three cases:

(4-1) Device never negates IORDY: No wait is generated.

(4-2) Device starts to drive IORDY low before tA, but causes IORDY to be asserted before tA: No wait generated.

(4-3) Device drives IORDY low before tA: wait generated. The cycle completes after IORDY is reasserted. For cycles where a wait is generated and -IORD is asserted, the device shall place read data on D15-D00 for tRD before causing IORDY to be asserted.

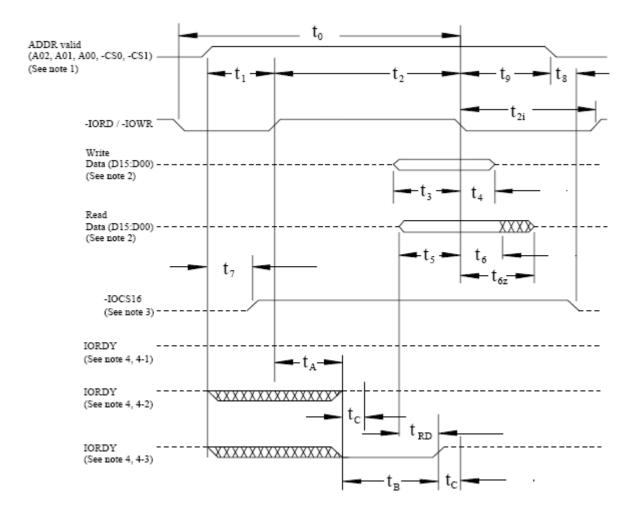

#### [Ultra DMA Mode 6]

| Name                 | Mode 0<br>(in ns) |     | Mode 1<br>(in ns) |     | Mode 2<br>(in ns) |     | Mode 3<br>(in ns) |     | Mode 4<br>(in ns) |     | Mode 5<br>(in ns) |     | Mode 6<br>(in ns) |     | Measurement<br>location |