# High-Voltage, Current-Mode, PWM Controller

#### Features

- 10 to 450V input voltage range

- <1.3 mA supply current

- >1 MHz clock

- · 49% maximum duty version

#### Applications

- Off-line high frequency power supplies

- · Universal input power supplies

- High density power supplies

- · Very high efficiency power supplies

- · Extra wide load range power supplies

#### Description

HV9120 and HV9123 are Switch-Mode Power Supply (SMPS) controllers suitable for the control of a variety of converter topologies, including flyback and forward converter.

Using an internal, high-voltage regulator, HV9120 and HV9123 can derive a bias supply for starting-up and powering a converter from a variety of power sources, such as a 12V battery or the rectified AC (230 VAC) line.

HV9120/HV9123 controllers include all essentials for a power-converter design, such as a bandgap reference, an error amplifier, a ramp generator, a high-speed PWM comparator, and a gate driver. A shutdown latch provides on/off control. Device power consumption is less than 6 mW when shutdown.

HV9120 offers 50% maximum duty and HV9123 offers nearly 100% duty.

#### Package Types

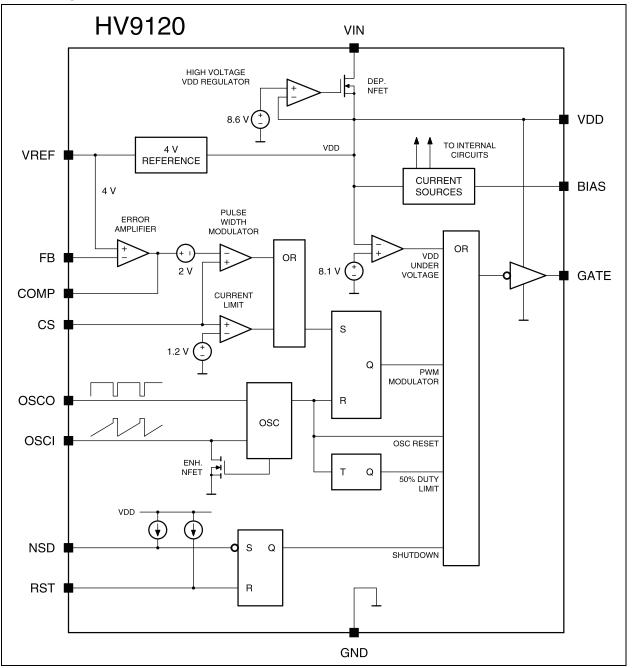

#### Block Diagram HV9120

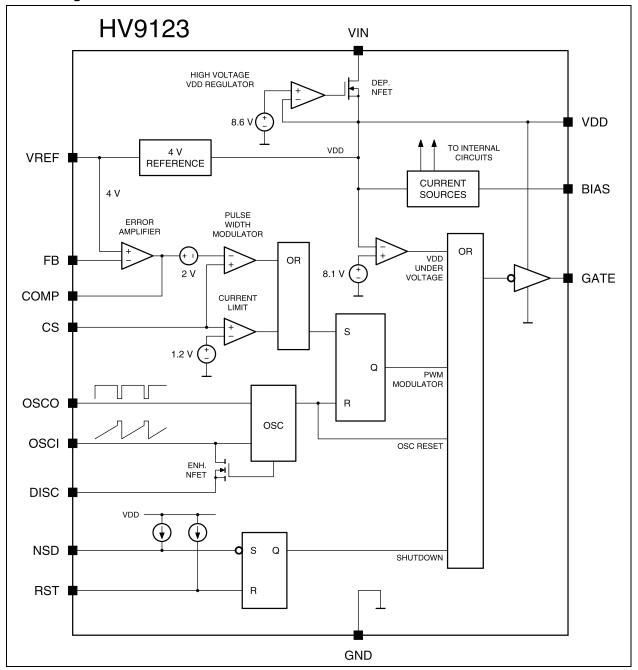

#### Block Diagram HV9123

#### 1.0 ELECTRICAL CHARACTERISTICS

#### **ABSOLUTE MAXIMUM RATINGS<sup>†</sup>**

| Input voltage, V <sub>IN</sub>                                     |                                |

|--------------------------------------------------------------------|--------------------------------|

| Device supply voltage, V <sub>DD</sub>                             | 15.5V                          |

| Logic input voltage                                                | 0.3V to V <sub>DD</sub> + 0.3V |

| Linear input voltage                                               | 0.3V to V <sub>DD</sub> + 0.3V |

| High-voltage regulator input current (continuous), I <sub>IN</sub> | 2.5 mA                         |

| Operating temperature range                                        | 40°C to +125°C                 |

| Storage temperature range                                          |                                |

| Power dissipation: 16-Lead SOIC                                    |                                |

| 16-Lead PDIP                                                       |                                |

**†** Notice: Stresses above those listed under "Maximum Ratings" may cause permanent damage to the device. This is a stress rating only and functional operation of the device at those or any other conditions above those indicated in the operational listings of this specification is not implied. Exposure to maximum rating conditions for extended periods may affect device reliability.

#### **ELECTRICAL CHARACTERISTICS**

| Electrical Specifications: $V_{DD}$ = 10V, $V_{IN}$ = 48V, $V_{DISC}$ = 0V, $R_{BIAS}$ = 390 k $\Omega$ , $R_{OSC}$ = 330 k $\Omega$ , $T_A$ = 25°C, unless of | 1- |

|----------------------------------------------------------------------------------------------------------------------------------------------------------------|----|

| erwise noted.                                                                                                                                                  |    |

| Parameter                          | Symbol    | Min                | Тур  | Max  | Units | Conditions |                                                              |

|------------------------------------|-----------|--------------------|------|------|-------|------------|--------------------------------------------------------------|

| Reference                          |           |                    | -    |      | •     | •          | •                                                            |

| Output voltage                     |           | V <sub>REF</sub>   | 3.92 | 4.00 | 4.08  | V          | R <sub>L</sub> = 10 MΩ                                       |

|                                    |           |                    | 3.84 | 4.00 | 4.16  |            | R <sub>L</sub> = 10 MΩ,                                      |

|                                    |           |                    |      |      |       |            | T <sub>A</sub> = -40°C to +125°C                             |

| Output impedance                   |           | Z <sub>OUT</sub>   | 15   | 30   | 45    | kΩ         | (Note 1)                                                     |

| Short circuit current              |           | I <sub>SHORT</sub> | -    | 125  | 250   | μA         | V <sub>REF</sub> = GND                                       |

| Change in V <sub>REF</sub> with te | mperature | $\Delta V_{REF}$   | -    | 0.25 | -     | mV/°C      | T <sub>A</sub> = -40°C to +125°C ( <b>Note 1</b> )           |

| Oscillator                         |           |                    |      |      |       |            |                                                              |

| Oscillator frequency               |           | f <sub>MAX</sub>   | 1.0  | 3.0  | -     | MHz        | R <sub>OSC</sub> = 0Ω                                        |

| Initial accuracy                   |           | f <sub>OSC</sub>   | 80   | 100  | 120   | kHz        | R <sub>OSC</sub> = 330 kΩ ( <b>Note 2</b> )                  |

|                                    |           |                    | 160  | 200  | 240   |            | R <sub>OSC</sub> = 150 kΩ ( <b>Note 2</b> )                  |

| VDD regulation                     |           | -                  | -    | -    | 15    | %          | 9.5V< V <sub>DD</sub> <13.5V                                 |

| Temperature coefficie              | nt        | -                  | -    | 170  | -     | ppm/°C     | T <sub>A</sub> = -40°C to +125°C ( <b>Note 1</b> )           |

| PWM                                |           |                    |      |      |       |            |                                                              |

| Maximum duty cycle                 | HV9120    | D <sub>MAX</sub>   | 49.0 | 49.4 | 49.6  | %          | (Note 1)                                                     |

|                                    | HV9123    |                    | 95   | 97   | 99    |            |                                                              |

| Dead time                          | HV9123    | D <sub>MIN</sub>   | -    | 225  | -     | ns         | HV9123 only (Note 1)                                         |

| Minimum duty cycle                 |           |                    | -    | -    | 0     | %          | -                                                            |

| Pulse width where pul              | se drops  |                    |      | 80   | 125   | ns         | (Note 1)                                                     |

| out                                |           |                    | -    | 00   | 125   | 115        |                                                              |

| Current Limit                      |           |                    |      |      |       |            |                                                              |

| Maximum input signal               |           | V <sub>LIM</sub>   | 1.0  | 1.2  | 1.4   | V          | V <sub>FB</sub> = 0V                                         |

| Delay to output                    |           | t <sub>D</sub>     | -    | 80   | 120   | ns         | V <sub>CS</sub> = 1.5V, V <sub>COMP</sub> ≤ 2.0V<br>(Note 1) |

#### **ELECTRICAL CHARACTERISTICS (CONTINUED)**

| erwise noted.                          |            | – 100, v <sub>IN</sub> = | 40V, VDIS                 | <sub>iC</sub> = uv, R <sub>E</sub> | <sub>3IAS</sub> = 390 | , K12, K <sub>OS</sub> | <sub>C</sub> = 330 kΩ, T <sub>A</sub> = 25°C, unless o       |

|----------------------------------------|------------|--------------------------|---------------------------|------------------------------------|-----------------------|------------------------|--------------------------------------------------------------|

| Parameter                              |            | Symbol                   | Min                       | Тур                                | Мах                   | Units                  | Conditions                                                   |

| Error Amplifier                        |            |                          |                           |                                    | •                     |                        | ·                                                            |

| Feedback voltage                       |            | V <sub>FB</sub>          | 3.92                      | 4.00                               | 4.08                  | V                      | FB shorted to COMP                                           |

| Input bias current                     |            | I <sub>IN</sub>          | -                         | 25                                 | 500                   | nA                     | V <sub>FB</sub> = 4.0V                                       |

| Input offset voltage                   |            | V <sub>OS</sub>          | null                      | ed during                          | trim                  | -                      | _                                                            |

| Open loop voltage gai                  | n          | A <sub>VOL</sub>         | 60                        | 80                                 | -                     | dB                     | (Note 1)                                                     |

| Unity gain bandwidth                   |            | GB                       | 1.0                       | 1.3                                | -                     | MHz                    | (Note 1)                                                     |

| Output source current                  |            | ISOURCE                  | -1.4                      | -2.0                               | -                     | mA                     | V <sub>FB</sub> = 3.4V                                       |

| Output sink current                    |            | I <sub>SINK</sub>        | 0.12                      | 0.15                               | -                     | mA                     | V <sub>FB</sub> = 4.5V                                       |

| High-voltage Regulat                   | tor and St |                          |                           |                                    |                       | •                      |                                                              |

| Input voltage                          |            | V <sub>IN</sub>          | 10                        | -                                  | 450                   | V                      | I <sub>IN</sub> < 10 μΑ; V <sub>CC</sub> > 9.4V              |

| Input leakage current                  |            | I <sub>IN</sub>          | -                         | -                                  | 10                    | μA                     | V <sub>DD</sub> > 9.4V                                       |

| Regulator turn-off thre voltage        | shold      | V <sub>TH</sub>          | 8.0                       | 8.7                                | 9.4                   | V                      | I <sub>IN</sub> = 10 μA                                      |

| Undervoltage lockout                   |            | V <sub>LOCK</sub>        | 7.0                       | 8.1                                | 8.9                   | V                      | -                                                            |

| Supply                                 |            |                          |                           |                                    |                       |                        | •                                                            |

| Supply current                         |            | I <sub>DD</sub>          | -                         | 0.75                               | 1.3                   | mA                     | C <sub>L</sub> < 75 pF                                       |

| Quiescent supply curre                 | ent        | I <sub>Q</sub>           | _                         | 0.55                               | -                     | mA                     | V <sub>NSD</sub> = 0V                                        |

| Nominal bias current                   |            | I <sub>BIAS</sub>        | _                         | 20                                 | -                     | μA                     | _                                                            |

| Operating range                        |            | V <sub>DD</sub>          | 9.0                       | -                                  | 13.5                  | V                      | _                                                            |

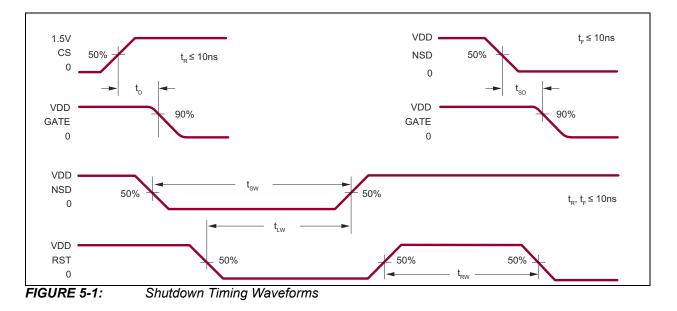

| Shutdown Logic                         |            | 66                       |                           | L                                  |                       | 1                      |                                                              |

| Shutdown delay                         |            | t <sub>SD</sub>          | -                         | 50                                 | 100                   | ns                     | C <sub>L</sub> = 500 pF, V <sub>CS</sub> = 0V (Note 1        |

| NSD pulse width                        |            | t <sub>SW</sub>          | 50                        | -                                  | -                     | ns                     | (Note 1)                                                     |

| RST pulse width                        |            | t <sub>RW</sub>          | 50                        | -                                  | -                     | ns                     | (Note 1)                                                     |

| Latching pulse width                   |            | t <sub>LW</sub>          | 25                        | _                                  | -                     | ns                     | V <sub>NSD</sub> , V <sub>RST</sub> =0V(Note 1)              |

| Input low voltage                      |            | V <sub>IL</sub>          | -                         | _                                  | 2.0                   | V                      |                                                              |

| Input high voltage                     |            | V <sub>IH</sub>          | 7.0                       | -                                  | _                     | V                      |                                                              |

| Input current, input hig               | h voltage  | I <sub>IH</sub>          | -                         | 1.0                                | 5.0                   | μA                     | V <sub>IN</sub> = V <sub>DD</sub>                            |

| Input current, input lov               | -          |                          | -                         | -25                                | -35                   | μA                     | V <sub>IN</sub> = 0V                                         |

| Output                                 | ronago     | 'IL                      |                           | 20                                 |                       | μ                      |                                                              |

| Output high voltage                    |            | V <sub>OH</sub>          | V <sub>DD</sub> -<br>0.25 | -                                  | -                     | V                      | I <sub>OUT</sub> = 10 mA                                     |

|                                        |            |                          | V <sub>DD</sub> -<br>0.3  | -                                  | -                     |                        | I <sub>OUT</sub> = 10 mA,<br>T <sub>A</sub> = -40°C to 125°C |

| Output low voltage                     |            | V <sub>OL</sub>          | -                         | -                                  | 0.2                   | V                      | I <sub>OUT</sub> = -10 mA                                    |

|                                        |            |                          | -                         | -                                  | 0.3                   | -                      | $I_{OUT}$ = -10 mA,<br>T <sub>A</sub> = -40°C to 125°C       |

| Output resistance Pull up<br>Pull down |            | R <sub>OUT</sub>         | -                         | 15                                 | 25                    | Ω                      | I <sub>OUT</sub> = ±10 mA                                    |

|                                        |            |                          | -                         | 8.0                                | 20                    | 1                      |                                                              |

|                                        | Pull up    |                          | -                         | 20                                 | 30                    | Ω                      | I <sub>OUT</sub> = ±10 mA,                                   |

|                                        | Pull down  |                          | -                         | 10                                 | 30                    | 1                      | T <sub>A</sub> = -40°C to 125°C                              |

| Rise time                              |            | t <sub>R</sub>           | -                         | 30                                 | 75                    | ns                     | C <sub>1</sub> = 500 pF ( <b>Note 1</b> )                    |

| Fall time                              |            | t <sub>F</sub>           | _                         | 20                                 | 75                    | ns                     | $C_1 = 500 \text{ pF}(\text{Note 1})$                        |

Note 1: Design guidance only; Not 100% tested in production.

2: Stray capacitance on OSC in pin must be  $\leq$  5 pF.

#### **TEMPERATURE SPECIFICATIONS**

| Parameter                   | Symbol          | Min | Тур | Max | Units | Conditions |

|-----------------------------|-----------------|-----|-----|-----|-------|------------|

| Temperature Ranges          |                 |     |     |     |       |            |

| Operating Temperature       |                 | -40 |     | 125 | °C    |            |

| Storage Temperature         |                 | -65 | _   | 150 | °C    |            |

| Package Thermal Resistances | •               |     |     |     | •     |            |

| Thermal Resistance, SOIC    | θ <sub>ja</sub> | -   | 83  | -   | °C/W  |            |

| Thermal Resistance, PDIP    | θ <sub>ja</sub> | _   | 51  | -   | °C/W  |            |

#### 1.1 Truth Table

#### TRUTH TABLE

| SHUTDOWN          | RESET             | OUTPUT                      |

|-------------------|-------------------|-----------------------------|

| Н                 | Н                 | Normal operation            |

| Н                 | $H \rightarrow L$ | Normal operation, no change |

| L                 | Н                 | Off, not latched            |

| L                 | L                 | Off, latched                |

| $L \rightarrow H$ | L                 | Off, latched, no change     |

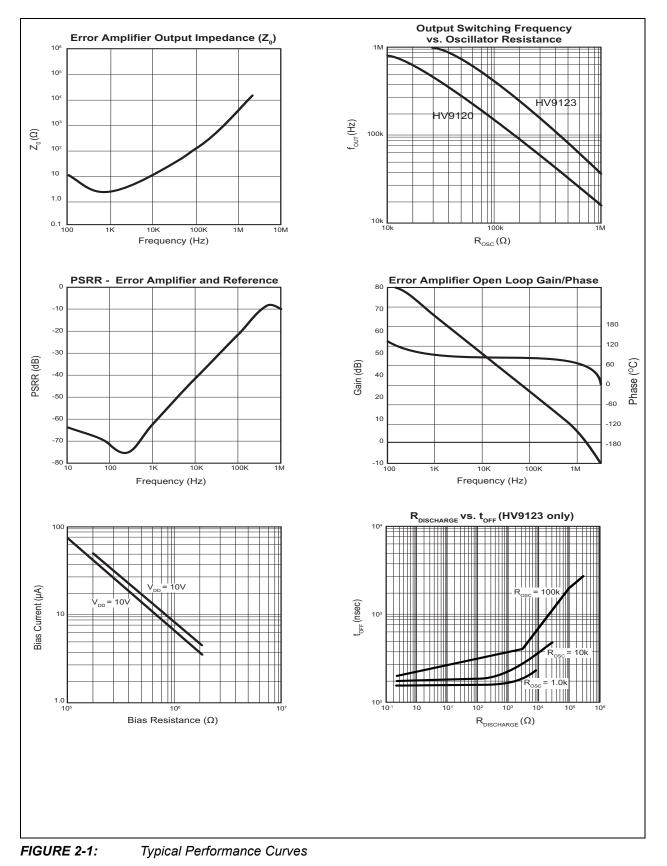

#### 2.0 TYPICAL PERFORMANCE CURVES

#### 3.0 PIN DESCRIPTION

The locations of the pins are listed in Features.

#### TABLE 3-1: PIN DESCRIPTION

| Pin # | Symbol HV9120   | Symbol HV9123   | Description                                                                                                         |

|-------|-----------------|-----------------|---------------------------------------------------------------------------------------------------------------------|

| 1     | V <sub>IN</sub> | V <sub>IN</sub> | High-voltage, V <sub>DD</sub> regulator input                                                                       |

| 2     | NC              | NC              | No connect                                                                                                          |

| 3     | NC              | NC              | No connect                                                                                                          |

| 4     | CS              | CS              | Current-sense input                                                                                                 |

| 5     | GATE            | GATE            | Gate-drive output                                                                                                   |

| 6     | GND             | GND             | Ground                                                                                                              |

| 7     | VDD             | VDD             | High-voltage, V <sub>DD</sub> regulator output                                                                      |

| 8     | OSCO            | OSCO            | Oscillator output                                                                                                   |

| 9     | OSCI            | OSCI            | Oscillator Input                                                                                                    |

| 10    | NC              | DISC            | Oscillator discharge, current set                                                                                   |

| 11    | VREF            | VREF            | 4V Reference output<br>Reference voltage level can be over-<br>ridden by an externally-applied volt-<br>age source. |

| 12    | NSD             | NSD             | Active low input to set shutdown latch                                                                              |

| 13    | RST             | RST             | Active high input to reset shutdown latch                                                                           |

| 14    | COMP            | COMP            | Error-amplified output                                                                                              |

| 15    | FB              | FB              | Feedback-voltage input                                                                                              |

| 16    | BIAS            | BIAS            | Internal bias, current set                                                                                          |

#### 4.0 TEST CIRCUITS

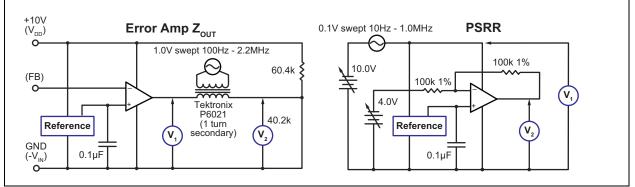

The test circuits for characterizing error-amplifier output impedance, Z<sub>OUT</sub>, and error-amplifier, power-supply rejection ration, PSRR, are shown in Figure 4-1.

FIGURE 4-1: Test Circuits

#### 5.0 DETAILED DESCRIPTION

#### 5.1 High-Voltage Regulator

The high-voltage regulator included in HV9120 and HV9123 consists of a high-voltage, n-channel, depletion-mode DMOS transistor, driven by an error amplifier, providing a current path between the V<sub>IN</sub> terminal and the V<sub>DD</sub> terminal. The maximum current, about 20 mA, occurs when V<sub>DD</sub> = 0, with current reducing as V<sub>DD</sub> rises. This path shuts off when V<sub>DD</sub> rises to somewhere between 7.8 and 9.4V. So, if V<sub>DD</sub> is held at 10 or 12V by an external source, no current other than leakage is drawn through the high voltage transistor. This minimizes dissipation.

Use an external capacitor between  $V_{DD}$  and GND to store energy used by the chip in the time between shutoff of the high voltage path and the  $V_{DD}$  supply's output rising enough to take over powering the chip. This capacitor should have a value of 100X or more the effective gate capacitance of the MOSFET being driven, as well as very good high-frequency characteristics. See the equation below. Ceramic caps work well. Electrolytic capacitors are generally not suitable.

$C_{VDD} \ge 100 \times (\text{gate charge of FET at } 10V)$

The device uses a resistor divider string to monitor  $V_{DD}$  for both the under voltage lockout circuit and the shutoff circuit of the high voltage FET. Setting the under voltage sense point about 0.6V lower on the string than the FET shutoff point guarantees that the under voltage lockout releases before the FET shuts off.

#### 5.2 Bias Circuit

HV9120 and HV9123 require an external bias resistor, connected between the BIAS pin and GND, to set currents in a series of current mirrors used by the analog sections of the chip. The nominal external bias current requirement is 15 to 20 μA, which can be set by a 390 kΩ to 510 kΩ resistor if V<sub>DD</sub> = 10V, or a 510 kΩ to 680 kΩ resistor if V<sub>DD</sub> = 12V. A precision resistor is not required, ±5% meets the device requirements.

#### 5.3 Clock Oscillator

The clock oscillator of the HV9120 and HV9123 consists of a ring of CMOS inverters, timing capacitors, and a capacitor-discharge FET. A single external resistor between the OSCI and OSCO sets the oscillator frequency (see Figure 2-1, Output Switching Frequency vs Oscillator Resistance).

HV9120 includes a frequency-dividing flip-flop that allows the part to operate with a 50% duty limit. Accordingly, the effective switching frequency of the power

converter is half the oscillator frequency (see Figure 2-1, Output Switching Frequency vs Oscillator Resistance).

An internal, discharge FET resets the oscillator ramp at the end of the oscillator cycle. The FET is internally connected to GND in HV9120 (50% max duty version). Whereas, the FET is externally connected to GND, by way of a resistor, in the HV9123 (100% duty version). The resistor programs the oscillator dead time at the end of the oscillator period in HV9123 applications.

The oscillator turns off during shutdown to reduce supply current by about 150  $\mu A.$

#### 5.4 Reference

The reference of the HV9120 and HV9123 consists of a band-gap reference, followed by a buffer amplifier, which scales the voltage up to 4.0V. The scaling resistors of the buffer amplifier are trimmed during manufacture so that the output of the error amplifier, when connected in a gain of -1 configuration, is as close to 4.0V as possible. This nulls out the input offset of the error amplifier. As a consequence, even though the observed reference voltage of a specific part may not be exactly 4.0V, the feedback voltage required for proper regulation will be 4.0V.

An approximately 50 k $\Omega$  resistor is located internally between the output of the reference buffer amplifier and the circuitry it feeds–reference output pin and noninverting input to the error amplifier. This allows overriding the internal reference with a low impedance voltage source ≤6.0V. Using an external reference reinstates the input offset voltage of the error amplifier. Overriding the reference should seldom be necessary.

The reference of the HV9120 and HV9123 is a high impedance node, and usually there will be significant electrical noise nearby. Therefore, a bypass capacitor between the reference pin and GND is strongly recommended. The reference buffer amplifier is compensated to be stable with a capacitive load of 0.01 to  $0.1 \,\mu\text{F}$ .

#### 5.5 Error Amplifier

The error amplifier in HV9120 and HV9123 is a lowpower, differential-input, operational amplifier. A PMOS input stage is used, so the common mode range includes ground and the input impedance is high.

#### 5.6 Current Sense Comparators

HV9120 and HV9123 use a dual-comparator system with independent comparators for modulation and current limiting. This allows the designer greater latitude in compensation design, as there are no clamps, except ESD protection, on the compensation pin.

#### 5.7 Remote Shutdown

The NSD and RST pins control the shutdown latch. These pins have internal, current-source pull-ups so they can be driven from open drain logic. When not used they should be left open, or connected to  $V_{\text{DD}}$ .

#### 5.8 Output Buffer

The output buffer of HV9120 and HV9123 is of standard CMOS construction–P-channel pull-up and Nchannel pull-down. Thus, the body-drain diodes of the output stage can be used for spike clipping. External Schottky diode clamping of the output is not required.

#### 6.0 PACKAGING INFORMATION

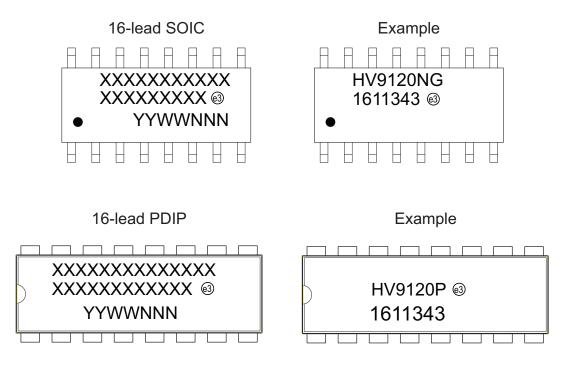

#### 6.1 Package Marking Information

| Legend | d: XXX<br>Y<br>YY<br>WW<br>NNN<br>@3<br>* | Product Code or Customer-specific information<br>Year code (last digit of calendar year)<br>Year code (last 2 digits of calendar year)<br>Week code (week of January 1 is week '01')<br>Alphanumeric traceability code<br>Pb-free JEDEC <sup>®</sup> designator for Matte Tin (Sn)<br>This package is Pb-free. The Pb-free JEDEC designator (e3)<br>can be found on the outer packaging for this package. |

|--------|-------------------------------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Note:  | be carrie<br>characters                   | nt the full Microchip part number cannot be marked on one line, it will<br>d over to the next line, thus limiting the number of available<br>s for product code or customer-specific information. Package may or<br>e the corporate logo.                                                                                                                                                                 |

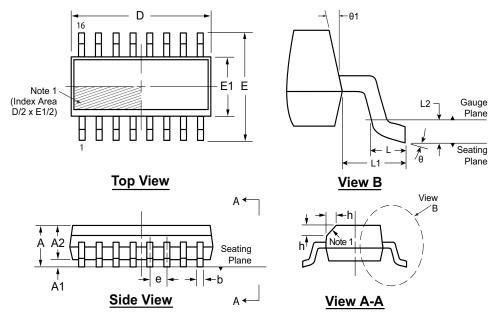

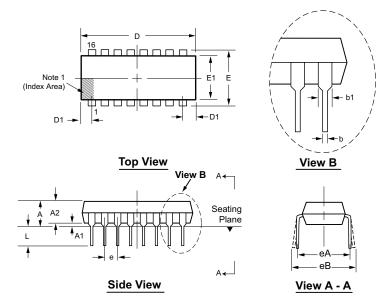

## 16-Lead SOIC (Narrow Body) Package Outline (NG)

9.90x3.90mm body, 1.75mm height (max), 1.27mm pitch

Note: For the most current package drawings, see the Microchip Packaging Specification at www.microchip.com/packaging.

Note:

1. This chamfer feature is optional. If it is not present, then a Pin 1 identifier must be located in the index area indicated. The Pin 1 identifier can be: a molded mark/identifier; an embedded metal marker; or a printed indicator.

| Symbo             | bl  | Α     | A1   | A2    | b    | D      | Е     | E1    | е           | h    | L    | L1          | L2          | θ          | θ1  |

|-------------------|-----|-------|------|-------|------|--------|-------|-------|-------------|------|------|-------------|-------------|------------|-----|

|                   | MIN | 1.35* | 0.10 | 1.25  | 0.31 | 9.80*  | 5.80* | 3.80* |             | 0.25 | 0.40 |             |             | <b>0</b> ° | 5°  |

| Dimension<br>(mm) | NOM | -     | -    | -     | -    | 9.90   | 6.00  | 3.90  | 1.27<br>BSC | -    | -    | 1.04<br>REF | 0.25<br>BSC | -          | -   |

| ()                | MAX | 1.75  | 0.25 | 1.65* | 0.51 | 10.00* | 6.20* | 4.00* | 200         | 0.50 | 1.27 |             | 200         | <b>8</b> 0 | 15° |

JEDEC Registration MS-012, Variation AC, Issue E, Sept. 2005. \* This dimension is not specified in the JEDEC drawing.

Drawings are not to scale.

## 16-Lead PDIP (.300in Row Spacing) Package Outline (P)

.790x.250in body, 210in height (max), .100in pitch

Note: For the most current package drawings, see the Microchip Packaging Specification at www.microchip.com/packaging.

Note:

1. A Pin 1 identifier must be located in the index area indicated. The Pin 1 identifier can be: a molded mark/identifier; an embedded metal marker; or a printed indicator.

| Symbo                 | ol  | Α     | A1    | A2   | b     | b1   | D     | D1    | Е     | E1   | е           | eA          | eВ    | L    |

|-----------------------|-----|-------|-------|------|-------|------|-------|-------|-------|------|-------------|-------------|-------|------|

|                       | MIN | .130* | .015  | .115 | .014  | .045 | .745† | .005  | .290† | .240 |             |             | .300* | .115 |

| Dimension<br>(inches) | NOM | -     | -     | .130 | .018  | .060 | .790  | -     | .310  | .250 | .100<br>BSC | .300<br>BSC | -     | .130 |

| (                     | MAX | .210  | .035* | .195 | .023† | .070 | .810† | .050* | .325  | .280 | 200         | 200         | .430  | .150 |

JEDEC Registration MS-001, Variation AB, Issue D, June, 1993.

\* This dimension is not specified in the JEDEC drawing. † This dimension differs from the JEDEC drawing. **Drawings not to scale.**

#### APPENDIX A: REVISION HISTORY

#### Revision A (May 2016)

- Updated file to Microchip format.

- Merged Supertex Doc #s DSFP-HV9120 and DSFP-HV9123 to Microchip DS20005519A.

- Revised Electrical Characteristics to accommodate the merged products.

- Updated Pin names to reflect new naming convention.

- Significant text changes to Detailed Description

- · Minor text changes throughout.

#### **PRODUCT IDENTIFICATION SYSTEM**

To order or obtain information, e.g., on pricing or delivery, refer to the factory or the listed sales office.

| PART NO.      | <u>xx</u> -                  | ¥ - ¥                                                                                                                                                                                                                        | E        | xamples:        |                                                                      |

|---------------|------------------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------|-----------------|----------------------------------------------------------------------|

| Device        | <br>Package Envin<br>Options | ronmental Media<br>Type                                                                                                                                                                                                      | a)<br>b) |                 | 14-Lead SOIC<br>package, 53/Tube<br>14-Lead SOIC<br>package, 53/Tube |

| Device:       | HV9120<br>HV9123             | <ul> <li>High Voltage Current-Mode PWM<br/>Controller, 10 to 450V input voltage range,<br/>49% duty cycle</li> <li>High Voltage Current-Mode PWM<br/>Controller, 9 to 80V input voltage range,<br/>99% duty cycle</li> </ul> | c)       | HV9123NG-G-M901 | 14-Lead SOIC<br>package, 2600/Reel                                   |

| Package:      | NG<br>P                      | = 16-lead SOIC<br>= 16-lead PDIP                                                                                                                                                                                             |          |                 |                                                                      |

| Environmental | G                            | = Lead (Pb)-free/ROHS-compliant package                                                                                                                                                                                      |          |                 |                                                                      |

| Media Type:   | (blank)<br>M901<br>M934      | <ul> <li>= 45/Tube for NG package<br/>24/Tube for P package</li> <li>= 2600/Reel for NG package</li> <li>= 2600/Reel for NG package</li> </ul>                                                                               |          |                 |                                                                      |

**Note:** For media types M901 and M934, the base quantity for tap and reel was standardized at 2600/reel. Both options will result in delivery of the same number of parts/reel.

#### Note the following details of the code protection feature on Microchip devices:

- · Microchip products meet the specification contained in their particular Microchip Data Sheet.

- Microchip believes that its family of products is one of the most secure families of its kind on the market today, when used in the intended manner and under normal conditions.

- There are dishonest and possibly illegal methods used to breach the code protection feature. All of these methods, to our knowledge, require using the Microchip products in a manner outside the operating specifications contained in Microchip's Data Sheets. Most likely, the person doing so is engaged in theft of intellectual property.

- Microchip is willing to work with the customer who is concerned about the integrity of their code.

- Neither Microchip nor any other semiconductor manufacturer can guarantee the security of their code. Code protection does not mean that we are guaranteeing the product as "unbreakable."

Code protection is constantly evolving. We at Microchip are committed to continuously improving the code protection features of our products. Attempts to break Microchip's code protection feature may be a violation of the Digital Millennium Copyright Act. If such acts allow unauthorized access to your software or other copyrighted work, you may have a right to sue for relief under that Act.

Information contained in this publication regarding device applications and the like is provided only for your convenience and may be superseded by updates. It is your responsibility to ensure that your application meets with your specifications. MICROCHIP MAKES NO REPRESENTATIONS OR WARRANTIES OF ANY KIND WHETHER EXPRESS OR IMPLIED, WRITTEN OR ORAL, STATUTORY OR OTHERWISE, RELATED TO THE INFORMATION, INCLUDING BUT NOT LIMITED TO ITS CONDITION, QUALITY, PERFORMANCE, MERCHANTABILITY OR FITNESS FOR PURPOSE. Microchip disclaims all liability arising from this information and its use. Use of Microchip devices in life support and/or safety applications is entirely at the buyer's risk, and the buyer agrees to defend, indemnify and hold harmless Microchip from any and all damages, claims, suits, or expenses resulting from such use. No licenses are conveyed, implicitly or otherwise, under any Microchip intellectual property rights unless otherwise stated.

### QUALITY MANAGEMENT SYSTEM CERTIFIED BY DNV = ISO/TS 16949=

#### Trademarks

The Microchip name and logo, the Microchip logo, dsPIC, FlashFlex, flexPWR, JukeBlox, KEELoQ, KEELoQ logo, Kleer, LANCheck, MediaLB, MOST, MOST logo, MPLAB, OptoLyzer, PIC, PICSTART, PIC<sup>32</sup> logo, RightTouch, SpyNIC, SST, SST Logo, SuperFlash and UNI/O are registered trademarks of Microchip Technology Incorporated in the U.S.A. and other countries.

The Embedded Control Solutions Company and mTouch are registered trademarks of Microchip Technology Incorporated in the U.S.A.

Analog-for-the-Digital Age, BodyCom, chipKIT, chipKIT logo, CodeGuard, dsPICDEM, dsPICDEM.net, ECAN, In-Circuit Serial Programming, ICSP, Inter-Chip Connectivity, KleerNet, KleerNet logo, MiWi, motorBench, MPASM, MPF, MPLAB Certified logo, MPLIB, MPLINK, MultiTRAK, NetDetach, Omniscient Code Generation, PICDEM, PICDEM.net, PICkit, PICtail, RightTouch logo, REAL ICE, SQI, Serial Quad I/O, Total Endurance, TSHARC, USBCheck, VariSense, ViewSpan, WiperLock, Wireless DNA, and ZENA are trademarks of Microchip Technology Incorporated in the U.S.A. and other countries.

SQTP is a service mark of Microchip Technology Incorporated in the U.S.A.

Silicon Storage Technology is a registered trademark of Microchip Technology Inc. in other countries.

GestIC is a registered trademark of Microchip Technology Germany II GmbH & Co. KG, a subsidiary of Microchip Technology Inc., in other countries.

All other trademarks mentioned herein are property of their respective companies.

© 2016, Microchip Technology Incorporated, Printed in the U.S.A., All Rights Reserved.

ISBN: 978-1-5224-0537-5

Microchip received ISO/TS-16949:2009 certification for its worldwide headquarters, design and wafer fabrication facilities in Chandler and Tempe, Arizona; Gresham, Oregon and design centers in California and India. The Company's quality system processes and procedures are for its PIC® MCUs and dsPIC® DSCs, KEELOQ® code hopping devices, Serial EEPROMs, microperipherals, nonvolatile memory and analog products. In addition, Microchip's quality system for the design and mulfacture of development systems is ISO 9001:2000 certified.

### **Worldwide Sales and Service**

#### AMERICAS

Corporate Office 2355 West Chandler Blvd. Chandler, AZ 85224-6199 Tel: 480-792-7200 Fax: 480-792-7277 Technical Support: http://www.microchip.com/ support

Web Address: www.microchip.com

Atlanta Duluth, GA Tel: 678-957-9614 Fax: 678-957-1455

Austin, TX Tel: 512-257-3370

Boston Westborough, MA Tel: 774-760-0087 Fax: 774-760-0088

**Chicago** Itasca, IL Tel: 630-285-0071 Fax: 630-285-0075

**Cleveland** Independence, OH Tel: 216-447-0464 Fax: 216-447-0643

**Dallas** Addison, TX Tel: 972-818-7423 Fax: 972-818-2924

**Detroit** Novi, MI Tel: 248-848-4000

Houston, TX Tel: 281-894-5983

Indianapolis Noblesville, IN Tel: 317-773-8323 Fax: 317-773-5453

Los Angeles Mission Viejo, CA Tel: 949-462-9523 Fax: 949-462-9608

New York, NY Tel: 631-435-6000

San Jose, CA Tel: 408-735-9110

**Canada - Toronto** Tel: 905-673-0699 Fax: 905-673-6509

#### ASIA/PACIFIC

Asia Pacific Office Suites 3707-14, 37th Floor Tower 6, The Gateway

Harbour City, Kowloon Hong Kong Tel: 852-2943-5100 Fax: 852-2401-3431

Australia - Sydney Tel: 61-2-9868-6733 Fax: 61-2-9868-6755

**China - Beijing** Tel: 86-10-8569-7000 Fax: 86-10-8528-2104

**China - Chengdu** Tel: 86-28-8665-5511 Fax: 86-28-8665-7889

China - Chongqing Tel: 86-23-8980-9588 Fax: 86-23-8980-9500

China - Dongguan Tel: 86-769-8702-9880

**China - Hangzhou** Tel: 86-571-8792-8115 Fax: 86-571-8792-8116

**China - Hong Kong SAR** Tel: 852-2943-5100 Fax: 852-2401-3431

**China - Nanjing** Tel: 86-25-8473-2460 Fax: 86-25-8473-2470

**China - Qingdao** Tel: 86-532-8502-7355 Fax: 86-532-8502-7205

**China - Shanghai** Tel: 86-21-5407-5533 Fax: 86-21-5407-5066

**China - Shenyang** Tel: 86-24-2334-2829 Fax: 86-24-2334-2393

**China - Shenzhen** Tel: 86-755-8864-2200 Fax: 86-755-8203-1760

**China - Wuhan** Tel: 86-27-5980-5300 Fax: 86-27-5980-5118

**China - Xian** Tel: 86-29-8833-7252 Fax: 86-29-8833-7256 ASIA/PACIFIC

**China - Xiamen** Tel: 86-592-2388138 Fax: 86-592-2388130

China - Zhuhai Tel: 86-756-3210040 Fax: 86-756-3210049

India - Bangalore Tel: 91-80-3090-4444 Fax: 91-80-3090-4123

India - New Delhi Tel: 91-11-4160-8631 Fax: 91-11-4160-8632

India - Pune Tel: 91-20-3019-1500

**Japan - Osaka** Tel: 81-6-6152-7160 Fax: 81-6-6152-9310

**Japan - Tokyo** Tel: 81-3-6880- 3770 Fax: 81-3-6880-3771

**Korea - Daegu** Tel: 82-53-744-4301 Fax: 82-53-744-4302

Korea - Seoul Tel: 82-2-554-7200 Fax: 82-2-558-5932 or 82-2-558-5934

Malaysia - Kuala Lumpur Tel: 60-3-6201-9857 Fax: 60-3-6201-9859

Malaysia - Penang Tel: 60-4-227-8870 Fax: 60-4-227-4068

Philippines - Manila Tel: 63-2-634-9065 Fax: 63-2-634-9069

**Singapore** Tel: 65-6334-8870 Fax: 65-6334-8850

**Taiwan - Hsin Chu** Tel: 886-3-5778-366 Fax: 886-3-5770-955

**Taiwan - Kaohsiung** Tel: 886-7-213-7828

**Taiwan - Taipei** Tel: 886-2-2508-8600 Fax: 886-2-2508-0102

**Thailand - Bangkok** Tel: 66-2-694-1351 Fax: 66-2-694-1350

#### EUROPE

Austria - Wels Tel: 43-7242-2244-39 Fax: 43-7242-2244-393

Denmark - Copenhagen Tel: 45-4450-2828 Fax: 45-4485-2829

France - Paris Tel: 33-1-69-53-63-20 Fax: 33-1-69-30-90-79

Germany - Dusseldorf Tel: 49-2129-3766400

Germany - Karlsruhe Tel: 49-721-625370

**Germany - Munich** Tel: 49-89-627-144-0 Fax: 49-89-627-144-44

**Italy - Milan** Tel: 39-0331-742611 Fax: 39-0331-466781

Italy - Venice Tel: 39-049-7625286

Netherlands - Drunen Tel: 31-416-690399 Fax: 31-416-690340

Poland - Warsaw Tel: 48-22-3325737

**Spain - Madrid** Tel: 34-91-708-08-90 Fax: 34-91-708-08-91

Sweden - Stockholm Tel: 46-8-5090-4654

**UK - Wokingham** Tel: 44-118-921-5800 Fax: 44-118-921-5820

07/14/15

# **Mouser Electronics**

Authorized Distributor

Click to View Pricing, Inventory, Delivery & Lifecycle Information:

Microchip: HV9120NG-G