## **SIEMENS**

#### Liability Exclusion

We have tested the contents of this document regarding agreement with the hardware and software described. Nevertheless, there may be deviations, and we don't guarantee complete agreement. The data in the document is tested periodically, however. Required corrections are included in subsequent versions. We gratefully accept suggestions for improvement

#### Copyright

Copyright © Siemens AG 1995. All Rights Reserved. Unless permission has been expressly granted, passing on this document or copying it, or using and sharing its content are not allowed. Offenders will be held liable. All rights reserved, in the event a patent is granted or a utility model or design is registered.

Subject to technical changes.

# **SIEMENS**

## <u>Releases</u>

| Release | Date       | Changes                                                                                                                                                                        |

|---------|------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| V 2.1   | Sept. 2003 | Description of the differences between the different manufacturers.<br>Specifications of the different manufacturers in chap. 7.1, 7.4 and 1.14<br>Chap 10.1 Contact addresses |

| V 2.2   | Dec 2005   | Included order numbers                                                                                                                                                         |

| V 2.3   | Apr 2009   | Remove data of the old ASIC                                                                                                                                                    |

| V 2.4   | May 2009   | Using of the ASPC2R                                                                                                                                                            |

## **Table of Contents**

| 1      | INTRODUCTION                                                                                                                                                                                                                                                                                                                                                                                                                                                               | 8                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  |

|--------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 1.1    | General                                                                                                                                                                                                                                                                                                                                                                                                                                                                    | 8                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  |

| 1.2    | Marketing the ASPC2 Software                                                                                                                                                                                                                                                                                                                                                                                                                                               | 8                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  |

| 1.3    | Overview of the ASICs                                                                                                                                                                                                                                                                                                                                                                                                                                                      | 10                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 |

| 1.4    | Application Field ASPC2                                                                                                                                                                                                                                                                                                                                                                                                                                                    | 11                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 |

| 1      | Notes.5.1ASPC2 Revision C1.5.1.1XWRL-XWRH Mode1.5.1.2Reset Input1.5.1.3CLK48 Input1.5.1.4Bus Access1.5.1.5Guranteed Operating Range1.5.1.6Version1.5.1.7Lock Handling1.5.1.8EOI Inactive Time1.5.1.9User Timer Interrupt1.5.1.10Blocked Mode1.5.1.11FIFO Size1.5.1.12Time between Two Tokens1.5.1.13NOP Request1.5.1.14Data Length5.2ASPC2 Revision D1.5.2.1Version1.5.2.3Deadlock Error if HW Wiring is Faulty5.3General Information1.5.3.1Daisy Chain1.5.3.28 Bit Access | 13         13         13         13         13         13         13         13         13         13         13         13         13         13         13         13         13         13         13         13         13         13         13         13         13         13         13         13         13         13         13         13         13         13         13         13         13         13         13         13         13         14         14         14         14         14         14         14         14 |

| 1.6    | Overview of the FLC Interface                                                                                                                                                                                                                                                                                                                                                                                                                                              | 15                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 |

| 1.7    | Function Overview                                                                                                                                                                                                                                                                                                                                                                                                                                                          | 17                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 |

| 1.8    | Address Assignment for the Peripheral Mode Interface                                                                                                                                                                                                                                                                                                                                                                                                                       | 18                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 |

| 1.9    | Pin Description                                                                                                                                                                                                                                                                                                                                                                                                                                                            | 20                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 |

| 1.1(   | 0 Pin Assignment                                                                                                                                                                                                                                                                                                                                                                                                                                                           | 22                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 |

| 1.11   | 1 Housing (P-MQFP100)                                                                                                                                                                                                                                                                                                                                                                                                                                                      | 23                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 |

| 1.12   | 2 Notes on Processing                                                                                                                                                                                                                                                                                                                                                                                                                                                      | 24                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 |

| 2      | FLC INTERFACE                                                                                                                                                                                                                                                                                                                                                                                                                                                              | 25                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 |

| 2<br>2 | System Control Block2.1.1Request Lists (BMH, BML)2.1.2CON IND HIGH, CON IND LOW or IND SEP HIGH, IND SEP LOW2.1.3CON SEP HIGH, CON SEP LOW2.1.4NOT OK HIGH, NOT OK LOW                                                                                                                                                                                                                                                                                                     | <b>25</b><br>25<br>27<br>27<br>28                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  |

## **SIEMENS**

| 2.1.5 SAP Lists (SM SAP, DEFAULT SAP, SAP [063])                          | 28              |

|---------------------------------------------------------------------------|-----------------|

| 2.2Structure of the Application Block2.2.1Appplication Block              | <b>32</b><br>32 |

| 2.3 Structure of the Lists                                                | 38              |

| 2.3.1 Request and SAP Lists                                               | 38              |

| 2.4 ASPC2 PROFIBUS Services                                               | 40              |

| 2.4.1 Send Data with No Acknowledge (SDN)                                 | 40              |

| 2.4.2 Send Data with Acknowledge (SDA)                                    | 40              |

| 2.4.3 Send and Request Data with Reply (SRD)                              | 40              |

| 2.4.4 Request FDL Status with Reply                                       | 40              |

| 3 BUS ACCESS PROTOCOL                                                     | 41              |

| 3.1 Token Management                                                      | 41              |

| 3.2 Layer 2 Setting                                                       | 42              |

| 3.2.1 PROFIBUS Mode                                                       | 42              |

| 3.2.2 PROFIBUS DP Support                                                 | 42              |

| 3.2.2.1 NOP Request                                                       | 42              |

| 3.2.2.2 DP Mode Parameterization                                          | 42              |

| 3.2.2.3 Consistency Support for the Master                                | 42              |

| 4 FUNCTION OF THE INDIVIDUAL BLOCKS                                       | 44              |

| 4.1 Processor Bus Interface                                               | 44              |

| 4.1.1 Bus Interface that can be Set                                       | 44              |

| 4.1.1.1 XWRL/XWRH Mode                                                    | 46              |

| 4.1.2 Master Mode                                                         | 46              |

| 4.1.2.1 SYS Bus Access<br>4.1.2.2 Quick Access Mode                       | 46              |

| 4.1.2.2 Guick Access Mode<br>4.1.2.3 Shared Memory                        | 46<br>48        |

| 4.1.2.4 Dual Port Memory                                                  | 48              |

| 4.1.3 Peripheral Mode                                                     | 50              |

| 4.1.4 SYS Bus Interface                                                   | 51              |

| 4.2 Parameter Register File                                               | 52              |

| 4.2.1 Operating Modes                                                     | 52              |

| 4.2.1.1 Mode Register 0                                                   | 57              |

| 4.2.1.2 Mode Register 1                                                   | 58              |

| <ul><li>4.2.1.3 Mode Register 2</li><li>4.2.1.4 Status Register</li></ul> | 59<br>61        |

| Ũ                                                                         | 01              |

| 4.3 Interrupt Controller                                                  | 64              |

| 4.4 Serial Interface                                                      | 67              |

| 4.4.1 Baudrate Generator                                                  | 67              |

| 4.4.2 Ser Bus Interface                                                   | 67              |

| 4.5 Delay Timer                                                           | 67              |

| 4.5.1 User Time Interrupt                                                 | 67              |

| 4.6 FIFO                                                                  | 68              |

| 4.6.1 Size of the FIFO                                                    | 68              |

| 4.6.2 Receive Mode                                                        | 68              |

#### ASPC 2 / Hardware User Description

Version V2.4

# **SIEMENS**

| 4.   | .6.3 Send Mode                                                                                                                                                                                           | 69                                      |

|------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----------------------------------------|

| 4.7  | LAS RAM                                                                                                                                                                                                  | 69                                      |

| 5    | TEST SUPPORT                                                                                                                                                                                             | 70                                      |

| 5.1  | Diagnostic Port                                                                                                                                                                                          | 70                                      |

| 6    | SPECIFICATION OF THE BUS TIMING                                                                                                                                                                          | 71                                      |

| 6.1  | Load of the Processor Interface with Hold Accesses                                                                                                                                                       | 71                                      |

| 6.2  | Dimensioning the Operating Parameters                                                                                                                                                                    | 72                                      |

| 7    | ELECTRICAL SPECIFICATION                                                                                                                                                                                 | 73                                      |

| 7.1  | Maximum Limits                                                                                                                                                                                           | 73                                      |

| 7.2  | Permissible Operating Values                                                                                                                                                                             | 73                                      |

| 7.3  | Guaranteed Operating Range for the Specified Parameters                                                                                                                                                  | 73                                      |

| 7.4  | DC Specification of the Pad Cells                                                                                                                                                                        | 74                                      |

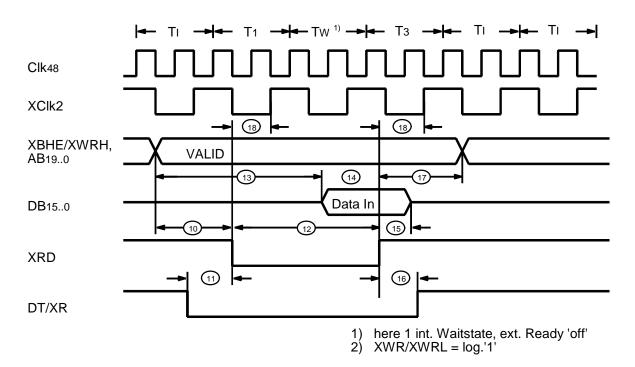

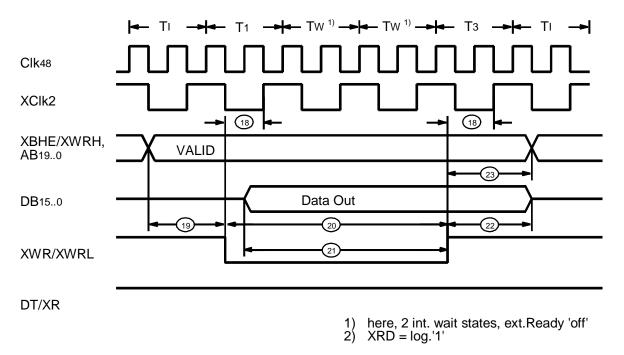

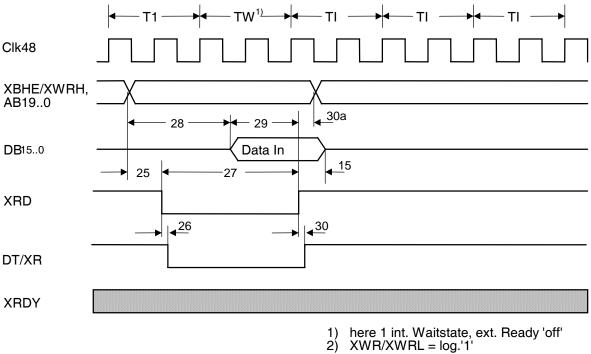

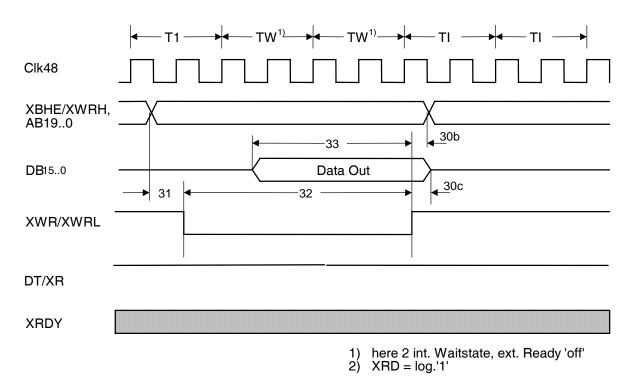

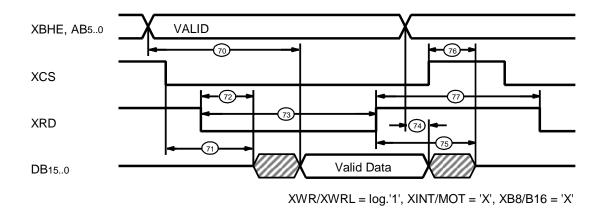

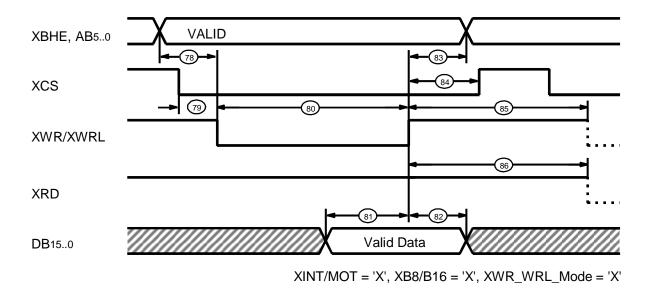

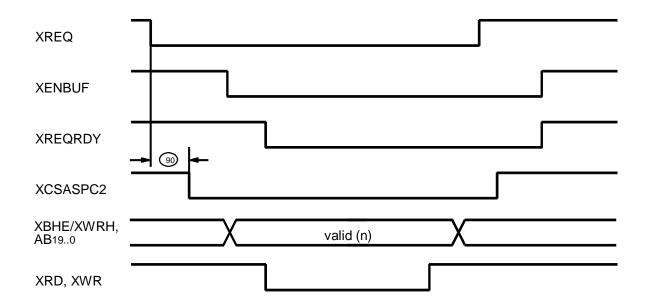

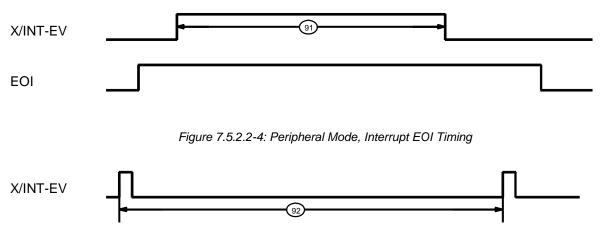

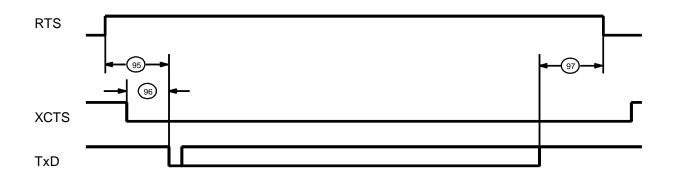

|      | AC Specifications<br>5.1 Driver Capability<br>5.2 Timing Diagrams, Signal Runtimes<br>7.5.2.1 SYS Bus Interface, Master Mode<br>7.5.2.2 SYS Bus Interface , Peripheral Mode<br>7.5.2.3 SER Bus Interface | <b>75</b><br>75<br>76<br>76<br>83<br>86 |

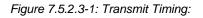

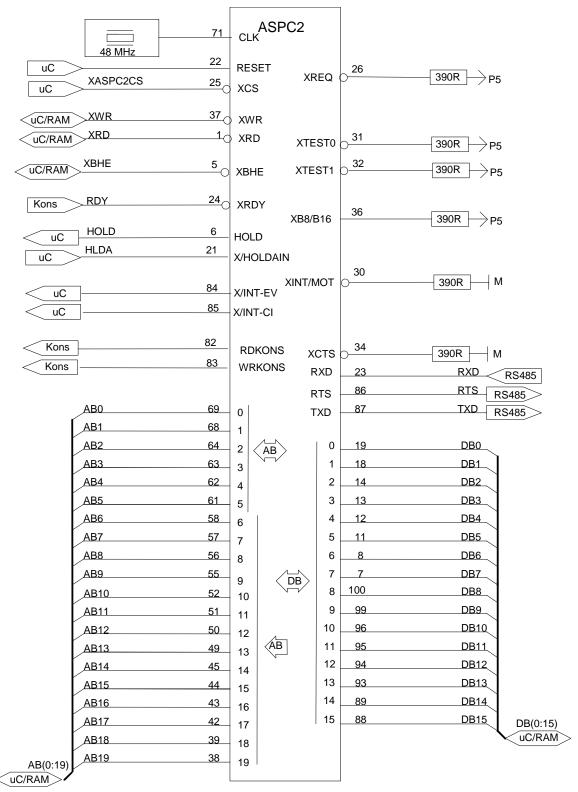

| 8    | EXAMPLE                                                                                                                                                                                                  | 87                                      |

| 8.1  | General                                                                                                                                                                                                  | 89                                      |

| 8.2  | Consistency Control                                                                                                                                                                                      | 89                                      |

| 8.3  | Comments                                                                                                                                                                                                 | 89                                      |

| 9    | PROFIBUS INTERFACE                                                                                                                                                                                       | 90                                      |

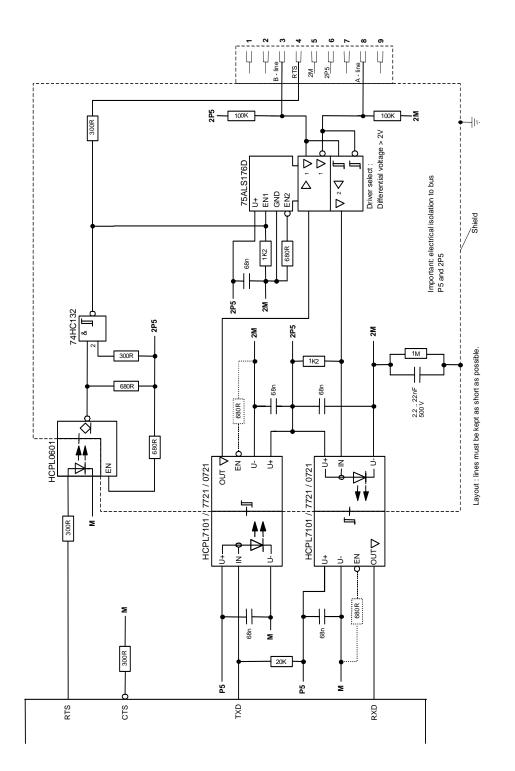

| 9.1  | Wiring Example RS485 Interface                                                                                                                                                                           | 90                                      |

| 9.2  | Pin Assignment                                                                                                                                                                                           | 91                                      |

| 9.3  | Connectors                                                                                                                                                                                               | 91                                      |

| 9.4  | Line Length                                                                                                                                                                                              | 91                                      |

| 10   | APPENDIX                                                                                                                                                                                                 | 92                                      |

| 10.1 | Addresses                                                                                                                                                                                                | 92                                      |

| 10.2 | 2 List of Abbreviations                                                                                                                                                                                  | 93                                      |

95

## 11 ORDER NUMBERS

05/09

## 1 Introduction

Note:

Because of the complexity of the ASIC ASPC2, it is urgently recommened to use the software package offered; this will avoid errors in ASIC handling. Support for software generation and software testing beyond information over the phone is not possible.

#### 1.1 General

For simple and fast digital data exchange between PLCs, Siemens offers to its users ASICs which, on the basis of PROFIBUS EN 50170, support or completely process data traffic between the individual automation stations.

In the **SPC2**, parts of Layer2 that execute the bus protocol are already integrated. For the remaining functions of Layer2 (interface service, management), an additional microprocessor is needed.

The **SPC3**, through the integration of the complete PROFIBUS DP protocol, relieves the processor considerably, and can be operated on the bus with 12Mbaud.

The **SPC4** makes the protocol types DP, FMS, and PA possible, and can be operated on the bus also with 12Mbaud.

The chips support the passive stations on the bus system, and filter out all outside messages, and faulty user messages.

However, in the field of automation, there are also simple devices such as switches, thermoelements, etc.. No microprocessor is needed to record their states.

For a low cost adaptation of these devices, an additional ASIC is available, called **LSPM2** (Lean Siemens Profibus Multiplexer). The ASICs process as slaves in the bus system. A master addresses the ASICs via Layer2 of the 7-layer model. After a faulty message was received, both autonomously generate the requested reply messages (according to EN 50 170, Part 3).

With the communication chip **ASPC2** (Advanced Serial PROFIBUS Controller), Layer1 and Layer2 is processed completely by PROFIBUS EN 50170. At the same time, the ASPC2 serves as a master for PROFIBUS DP and, via a segment coupler, also for PROFIBUS PA (process automation). All ASICs are available on the market, and can be ordered from Siemens branches.

## 1.2 Marketing the ASPC2 Software

For the ASIC ASPC2 as DP master, extensive software is available (approx. 64Kbyte). Obtaining the software is bound to a license contract.

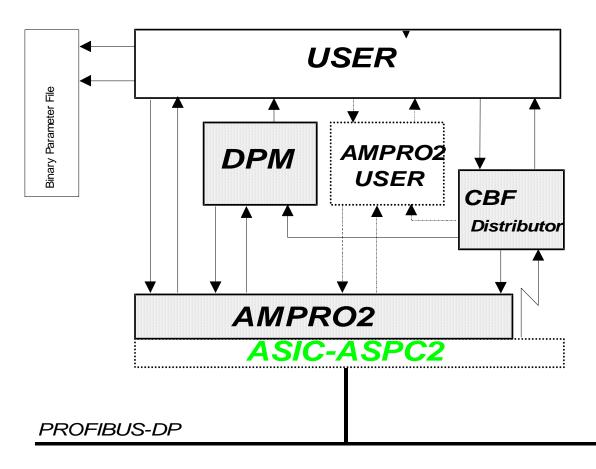

Software Structure

The figure below provides a short overview of the software of the master package. A detailed description is provided in the documentation **ASPC2 / Software**.

The software uses the structure of the binary parameter file of COM PROFIBUS

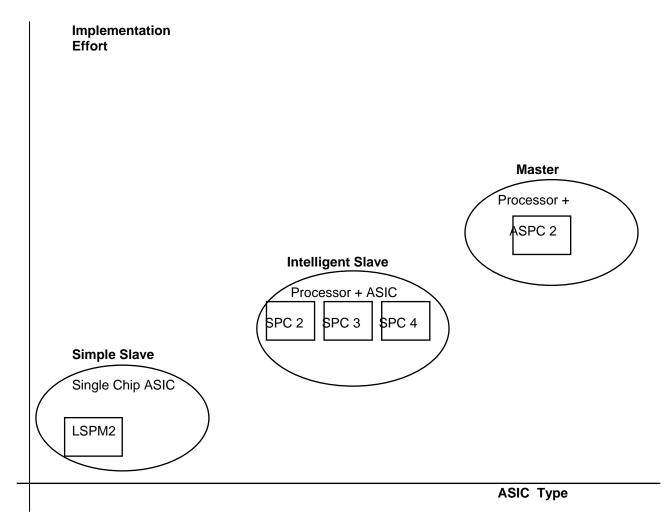

1.3 Overview of the ASICs

Figure 1.4-1: ASIC Overview

## 1.4 Application Field ASPC2

SIEMENS

The ASPC2 is the consistent continued development of the ASIC line for PROFIBUS.

With the communication chip ASPC2, Layer1 and Layer2 is processed entirely by PROFIBUS EN 50 170. At the same time, the ASPC2 serves as master for PROFIBUS DP, and, via a segment coupler, also for PROFIBUS PA.

This highly integrated controller chip is used in production engineering as well as in process engineering.

By using the ASPC2, the following are considerably relieved of tasks concerning communication processing: PLCs, PCs, drive controls, process control systems, up to operator interface systems.

To interface secondary devices -such as controllers, final controlling elements, transducers, and distributed peripherals- the PROFIBUS ASICs are used for slave appplications (refer to Figure 1.4-1).

#### Special Features of the ASPC2 ASIC:

- PROFIBUS DP, PROFIBUS FMS, and PROFIBUS PA are supported with a single chip

- High net data throughput

- Support of DP communication for the fastest response time

- Complete token management and job processing

- Optimum interfacing to available processor types

- No general conditions imposed on the microprocessor with respect to time

Interface to Host

- Processor Interface 8/16 bit can be set Intel/Motorola byte ordering can be set

- User Interface The ASPC2 can address 1 Mbyte externally as communication RAM

- Memory and microprocessor can be interfaced with the ASIC in the shared memory mode or in the dual port memory mode

- In the shared memory mode, equivalent operation of several ASPC2 on one microprocessor is possible

Supported Services

- Request-FDL-Status,

- Send Data with no Acknowledge (SDN) Broad/Multicast

- Send Data with Acknowledge (SDA)

- Send and Request Data with Reply (SRD)

Baudrates

- 9.6; 19.2; 45.45; 93.75; 187.5; 500, 750 kbit/s;

- 1.5; 3; 4; 6 and 12 Mbit/s

## Response Time

- Short acknowledgement; for example, SDA starting at 1 msec (11 bit timing)

- Typical, for example SRD starting at 3 msec

## Number of Stations

- 126 active/passive, mixed as required

- 64 service access points and one default SAP

## Transmission Procedure according to

• PROFIBUS Standard EN 50 170 Volume 2

## Ambient temperatures

- Operating temperature -40 °C ... + 85 °C

- Storage temperature -65 °C ... +150 °C

- Chip temperature in operation  $-40 \ ^{\mathrm{O}}\mathrm{C} \ \dots +125 \ ^{\mathrm{O}}\mathrm{C}$

## **Constructive Design**

| ٠ | P-MQFP 100 Case |    | 14 x 20 mm <sup>2</sup>     |

|---|-----------------|----|-----------------------------|

|   |                 | or | 17.2 x 23.2 mm <sup>2</sup> |

## 1.5 Notes

## 1.5.1 ASPC2 Revision C

This ASIC differs only little fom its predecessor so that, because of its advantages, it can directly replace Revision B, provided the following points are noted:

## 1.5.1.1 XWRL-XWRH Mode

This mode can no longer be parameterized via Mode Register 1, but is set by connecting Pin 33. The previous function as test output is applied to Pin 35.

- Pin 33 is provided with an integrated pull-up resistor, so that if unconnected, as in the case of Revision B, the XBHE/XWR mode is switched on after reset.

- The when using the test mode, the pin change is to be taken into account.

- The bit in Mode Register 1 now has a different meaning.

## 1.5.1.2 Reset Input

This input is designed as CMOS Schmitt Trigger. At reset, the RTS output becomes immediately inactive.

## 1.5.1.3 CLK48 Input

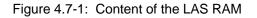

This input is designed as CMOS Schmitt Trigger. The pulse duty factor is distorted, and can now amount to 80/20 or 20/80.

## 1.5.1.4 Bus Access

The ASIC has a faster data transfer cycle time and, with a setting in Mode Register 2, can be operated in the quick access mode. With this, a further enhancement is attained.

## 1.5.1.5 Guranteed Operating Range

| Temperature Range |   | -40 C to +85 C |

|-------------------|---|----------------|

| DC Supply Voltage | : | +5V ±10 %      |

## 1.5.1.6 Version

The version can be read from the address 0BH. Revision B (value = 0), or Revision C (value = 1)

## 1.5.1.7 Lock Handling

In the dual port memory mode, the user can set the lock handling of the ASPC2.

## 1.5.1.8 EOI Inactive Time

The time between EOI and the next possible interrupt can be parameterized for 1  $\mu$ s, or 1 ms (another time base applies to the monitor mode).

## 1.5.1.9 User Timer Interrupt

With the delay timer, the user can implement a software timer that can be set to 2.1 sec, or 10 msec via Mode Register 2.

## 1.5.1.10 Blocked Mode

With this setting, input data that is less than the FIFO size can be held back in the FIFO until the entire message is received and was checked for correctness. This function depends no longer on the DP mode setting, but on a setting in Mode Register 2.

## 1.5.1.11 FIFO Size

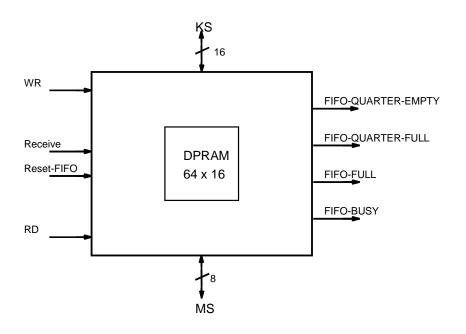

The FIFO size can be set for 64 (as in Revision B), or 128 bytes in Mode Register 2.

## 1.5.1.12 Time between Two Tokens

In the pass token mode, there now is a wait of Tid1 between two successive token messages to itself.

#### 1.5.1.13 NOP Request

Requests that are provided with this option are no longer sent (for example, FORCE PASS TOKEN request).

## 1.5.1.14 Data Length

If the L2 and L4 data length results in a value larger than 250D, the request is confirmed directly with 8EH, without sending a message.

If, at the slave, the received data length is less than the specified L4 length, the reply is now 'RS'.

#### 1.5.2 ASPC2 Revision D

The current shipping version of the ASIC ASPC2 is Revision D. For that reason, all values, tables, and documentation is laid out for Revision D.

The ASPC2 Revision C can be directly replaced with Revision D. However, a few points have to be noted.

#### 1.5.2.1 Version

The version can be read from Address 0BH. Revision C (value = 1) or Revision D (value = 2)

## 1.5.2.2 GAP Error in the DP Mode

Under certain circumstances the wrong GAP area is processed in the DP mode. This error has been removed in Revision D.

## 1.5.2.3 Deadlock Error if HW Wiring is Faulty

If, through faulty HW wiring, the access of the ASPC2 to the request data block was prevented through ready delay (approx. 15  $\mu$ s at 12 Mbaud), a deadlock could occur in Revision C. This deadlock has been removed in Revision D.

#### 1.5.3 General Information

## 1.5.3.1 Daisy Chain

If several ASICs are chained with a daisy chain, all chips have to be supplied synchronously with the same clock pulse.

## 1.5.3.2 8 Bit Access

In the case of read accesses in the 8 bit mode, the output signal DTXR can remain on log. 1 if slow bus mode and dual port memory mode is set.

## 1.6 Overview of the FLC Interface

The ASPC2 is the **MAC** (Medium Access Controller) that carries out the bus protocol of Layer 2. The remaining functions of Layer2 (interface service, management) are handled by the **FLC software** (Field Link Controller). The FLC connects the user and the ASPC2 (MAC).

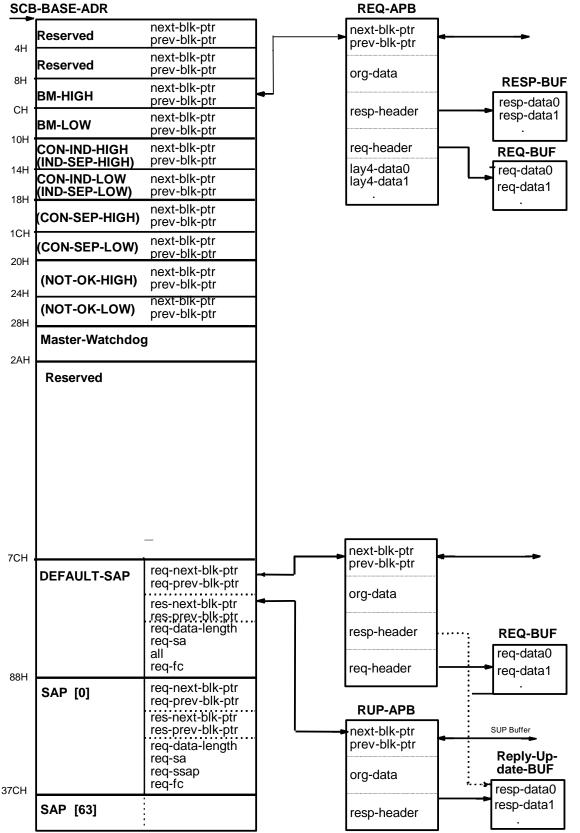

The **System Control Block, SCB** (refer to Figure 1.7) is used as the interface between the ASPC2 and the FLC. The SCB has to be established completely by the FLC. The FLC chains send requests in the **request lists**. Then, the ASPC2 processes these requests, removes them from the request lists, and enters them, depending on parameter assignment, either in the **CON IND lists (high or low)**, or **CON SEP or NOT OK lists (high or low)**. With interrupt, the FLC is informed of each request that was processed (confirmation). In the receive mode, the FLC makes up to **64 service access points (SAP[0] ... [63])** available to which the FLC loads receive requests (response data), and the ASPC2 stores the request data. An additional service access point is available as **default SAP**, if no DSAP address is specified in the call message. After a receive request has been processed successfully, it is removed from the corresponding **SAP list**, and chained in the **CON IND lists (high or low)** or **IND SEP lists (high or low)**. Here also, the FLC is informed with an interrupt (indication).

Send and receive requests are made available in **applicaton blocks**. These contain branching pointers, management data, the **request header including Layer4 data**, and the **response header**. **Request** and **response data** is available in separate buffers respectively.

The ASPC2 can address a 1Mbyte memory area directly. In that case, it is in the master mode. The handshake between the ASPC2 and an external bus master (for example, processor) is based on the **HOLDX/HOLDA signals**. For supporting dual port memory configurations, the ASPC2 has a bus arbiter which allocates the bus upon the request of an external bus partner. For parameter assignment and interrupt event handling, the ASPC2 is addressed by the processor in the peripheral mode by writing to diverse ASPC2 registers, or reading them. In addition, the processor has to make one or -in the case of CON/IND and error event handling- two interrupt inputs available.

The bus access is a hybrid method, **token passing**. Token management in the ASPC2 is completely autonomous. Fault modes and special operating modes are controlled by the chip.

A total of 127 stations, active, passive, or mixed as needed, can be connected to the bus. The ASPC2 supports the **following services**:

- o Request-FDL Status

- Send Data with no Acknowledge, SDN (Broadcast/Multicast)

- Send Data with Acknowledge, SDA

- o Send and Request Data with Reply, SRD

Figure 1.7-1: System Control Block (SCB) of the ASPC2 (Intel Format)

## 1.7 Function Overview

The ASPC2 has a multiplexed bus interface (8/16 bit bus width) which can be set to Intel/Motorola. In the master mode, it becomes active itself, and transfers data from/to the memory (byte by byte, or word by word). For the memory access, 1 to 5 wait states can be set. In addition, the **Bus Interface Unit (BIU)** can process asynchronously, with external ready. Furthermore, a fast bus mode is implemented (quick access mode). The addressing space consists of 1Mbyte. In the shared memory mode, several ASPC2s can be interconnected via a daisy chain. To support dual port memory configurations, the ASPC2 has a bus arbiter to which an external bus master can be connected (XREQ). In the peripheral mode, the ASPC2 is addressed by the processor directly via a little address window. This mode is used for parameter assignment and interrupt event handling.

In the **parameter register file**, and in the **mode registers**, protocol-specific parameters are to be transferred by the processor after switch-on (diverse idle timing, station addresses, baudrate, etc.). In the **status register**, the *MAC status* can be polled any time.

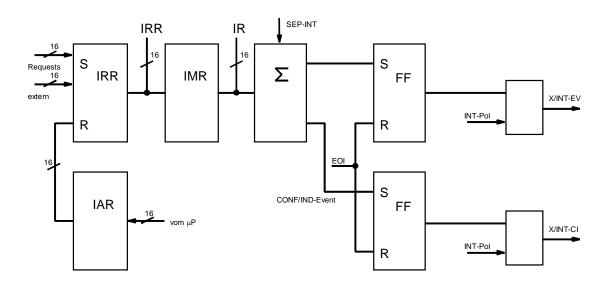

In the **interrupt controller**, various events are entered (such as error events, *MAC states*, etc.). These events can be enabled individually via a mask register. The acknowledgement is made via the acknowledge register. The ASPC2 has two innterrupt outputs: one for the confirmation/indication message only, and the other for error events.

The **Token Rotaton Timer** controls the token cycle time. The user parameterizes the token target rotation time (TTR), and is a multiple of 256 x tBit.

The **FIFO** (64/256Byte) is used as temporary buffer for the receive and send messages. It is controlled in the half duplex mode, and behaves according to the transfer direction in the SER bus. The ASIC transfers data between UART and FIFO, and the BIU between FIFO and the external memory. The SYS bus is obtained only if the content of the FIFO exceeds the quarter-full threshold, or undershoots the quarter-empty threshold. Thus, the data will be transferred only package by package.

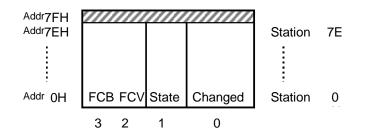

In the LAS RAM (128 x 4 bits), the list of the active stations is stored. Each active station has to carry this list in order to ensure faultless token traffic. In addition, the call sequence bits are stored in the LAS RAM for each bus station ( they prevent message loss or message duplication).

In the **UART**, the parallel data stream is converted into a serial data stream, and vice versa. The transmission procedure is asynchronous with startbit, 8 data bits, parity bit, and stop bit. The baudrate has to be parameterized at initialization. Baudrates in the range of from 9.6 kBd to 12MBd are permissible (refer to Table 4.2-1).

The **idle timer** checks the idle phase (binary '1') directly on the bus line, the Syn time that is necessary prior to a call for clear synchronization of the receivers. At the passive and the active station without a token, this timer is loaded with TSYN. At the active station with token, TID1 or TID2 is loaded, depending on the transmission service.

The **syni timer** monitors the transmission medium. If there is no receiver synchronization within the time TSYNI, there is a continuous malfunction. In this case, the MAC returns to the *not hold token mode*, and generates an error interrupt.

The **slot timer** monitors -at the active station with token after a call or token passing- whether the receiving station responds within the specified time TSLOP, or shows activity. If the timer expires, a repetition or a new message cycle is initiated. In the case of passive or active stations without token, the time TSLOT is used as count interval for the timeout timer.

The **timeout timer** monitors the bus activity of the active and passive stations. The TTIMEOUT is a multiple of the TSLOT in dependence on the station address. If the SER bus is idle during this time, there is a token loss which triggers (re)initialization at the active station.

## **1.8 Address Assignment for the Peripheral Mode Interface**

For parameter assignment and event handling, the processor has to address the ASPC2 in the peripheral mode. For this, a small address window of 64 bytes is available (refer to Table 1.9-1). An ASPC2 register is selected only if the 'XCS signal' and the corresponding offset address is applied.

| Read                                   |                     | Write                                  |                  |                        | OFF-ADDR          |

|----------------------------------------|---------------------|----------------------------------------|------------------|------------------------|-------------------|

| High(A0=1,XBHE=0)<br>High(A0=0,XBHE=1) |                     | High(A0=1,XBHE=0)<br>High(A0=0,XBHE=1) |                  | ).XBHE=1)<br>I,XBHE=0) | Intel<br>Motorola |

| TTHOLD158                              | TTHOLD158 TTHOLD 70 |                                        | TTR70            |                        | 00H               |

| Delay Timer158                         | Delay Timer70       | INT-MASK-REG 158                       | INT-MASP         | K-REG 70               | 02H               |

| INT-REQ-REG 158                        | INT-REQ-REG 70      | INT-REQ-REG 158                        | INT-REQ-F        | REG 70                 | 04H               |

| INT-REG 158                            | INT-REG 70          | INT-ACK-REG 158                        | INT-ACK-         | REG 70                 | 06H               |

| Status-REG158                          | Status-REG 70       | Mode-REG0158                           | Mode-RE          | <b>GO</b> 70           | 08H               |

| Status-REG 3124                        | Status-REG 2316     | Mode-REG1-Set 158                      | Mode-RE          | G1-Set 70              | 0AH               |

| -                                      | LAS-REG 30          | Mode-REG1-Res 158                      | Mode-RE          | G1-Res 70              | 0CH               |

|                                        |                     | SCB-BASE-LW 158                        | SCB-BAS          | E-LW 70                | 0EH               |

|                                        |                     | SCB-BASE-HW 3124                       | SCB-BAS          | E-HW 2316              | 10H               |

|                                        |                     | TSLOT-REG 138                          | TSLOT-RI         | E <b>G</b> 70          | 12H               |

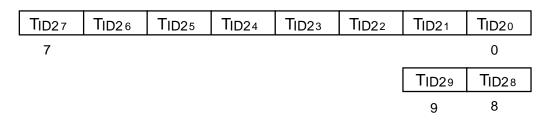

|                                        |                     | TID1-REG 98                            | TID1-REG         | i 70                   | 14H               |

|                                        |                     | TID2-REG 98                            | TID2-REG         | 70                     | 16H               |

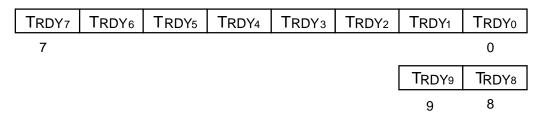

|                                        |                     | TRDY-REG 98                            | TRDY-RE          | <b>G</b> 70            | 18H               |

|                                        |                     | BR-REG 108                             | BR-REG 70        |                        | 1AH               |

|                                        |                     | SAP-MAX 70                             | TS-ADDR-REG 60   |                        | 1CH               |

|                                        |                     | Token-Err- 70                          | GUD-REG 70       |                        | 1EH               |

|                                        |                     | TQUI-REG 70                            | LAY4-HLen-REG 70 |                        | 20H               |

|                                        |                     | Resp-Err- 30                           | HSA 60           |                        | 22H               |

|                                        |                     |                                        | Reserved         | 1                      | 24H               |

|                                        |                     | Mode-REG250                            | Retry<br>Tok 30  | Retry<br>Msg 30        | 26H               |

|                                        |                     | WAIT STATES 158                        | WAIT STATES 70   |                        | 28H               |

|                                        |                     |                                        |                  |                        |                   |

Table 1.9-1: ASPC2 Internal Registers

#### Token Rotation Timer (Register):

The setpoint rotation time is parameterized (TTR). For system initialization, the token holding time (TTHOLD) can be read out.

#### Interrupt Controller Register:

The meaning of these registers will be explained in Chapter 4.3.

#### Status Register:

The meaning of this register is described in Chapter 4.2.1.4.

#### LAS Register:

Via this register, the processor can read out the LAS RAM. Each access increments the internally generated LAS RAM address (Chapter 4.7).

#### Mode Register:

The mode registers 0, 1, and 2 are used for parameterizing individual bits. The meaning is described in Chapter 4.2.1.

#### SCB BASE HW/LW

The 20/32 bit address of the system control block is parameterized (Chapter 4.2.1).

#### Slot Timer Register

The wait for receive time TDL is parameterized (Chapter 4.2.1).

#### **Idle Timer Register**

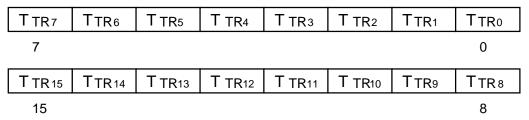

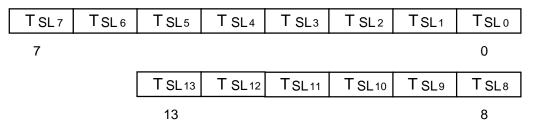

The follwing timing is parameterized (Chapter 4.2.1):

- TID1 (valid after acknowledgement, response, or token messages)

- TID2 (valid after a call message that is not acknowledged)

- TRDY (ready time, valid prior to sending a reply message)

#### **Baudrate Register**

The scaling factor is parameterized (Chapter 4.2.1).

#### **TS Address Register**

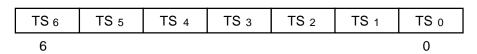

The station address is parameterized (Chapter 4.2.1).

#### **GUD Register**

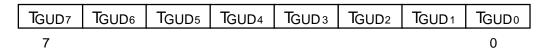

The GAP updating time TGUD is parameterized (Chapter 4.2.1).

#### **Token Error Limit Register**

The number of unvalidated token messages per 256 token rotations is parameterized, before the ASPC2 enters the *listen token mode* (Chapter 4.2.1).

#### SAP MAX Register

The highest SAP list number generated in the SCB is parameterized (Chapter 4.2.1).

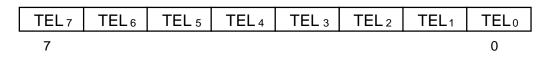

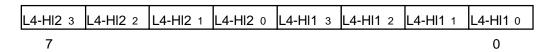

#### LAY4 Hlen Register

Two different Layer4 header lengths are parameterized (Chapter 4.2.1).

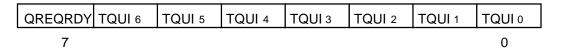

#### **TQUI Register**

The modulator fading time TQUI is parameterized (Chapter 4.2.1). In addition, the delay time between XENBUF and XREQRDY is set (Chapter 4.1.2).

#### **HSA Register**

The highest active address is parameterized (Chapter 4.2.1).

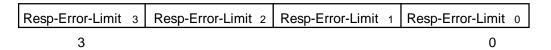

#### **Response Error Limit Register**

The number of faulty response messages is parameterized, according to which double token is assumed (Chapter 4.2.1).

#### **Reserved Register**

In the reserved register, the early setting of RTS for TxD is parameterized (Chapter 4.2.1).

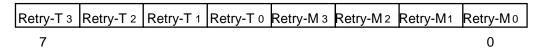

#### **Retry Register**

The number of message and token repetitions is parameterized (Chapter 4.2.1).

#### Wait States Register

The wait states for each 256K memory segment are parameterized (Chapter 4.2.1).

#### **Delay Timer**

The meaning of this timer is described in Chapter 4.5.

## 1.9 Pin Description

The ASPC2 has an R-PQFP G100 pin case with the following signals:

#### 11 Inputs:

| Signal Name Quantity                                                                          |                                                | Function                                                                                                                                                                                                                             | Source                                                                                                                                                                      |  |

|-----------------------------------------------------------------------------------------------|------------------------------------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|

| CLK*<br>RESET*<br>XCS<br>XRDY<br>X/HOLDAIN<br>XREQ<br>RxD<br>XCTS<br>XB8/B16**<br>XINT/MOT*** | 1<br>1<br>1<br>1<br>1<br>1<br>1<br>1<br>1<br>1 | Clock Input (48MHz)<br>Hardware Reset<br>Chip Select<br>Asynchronous Ready<br>Hold Acknowledge In<br>Bus Request from ext. master<br>Serial receive channel<br>Clear to Send<br>System bus configuration<br>System bus configuration | System Support<br>CPU, Port<br>System Support<br>System Support<br>CPU or previous AMPlus<br>System Support<br>RS 485 Receiver<br>FSK Modem<br>Sold. Jumper<br>Sold. Jumper |  |

| XWRL-MODE**                                                                                   | 1                                              | 80C165-Interface: XWRH, XWRL                                                                                                                                                                                                         | Sold. Jumper                                                                                                                                                                |  |

\* CMOS Schmitt Trigger Input

\*\* CMOS input with integrated pull-up\*\*\* CMOS input with integrated pull-down

Table 1.10-1: Input Pins of the ASPC2 (without test inputs)

#### 35 Outputs

| Signal Name                                                                                                 | Quantity                                                                          | Function                                                                                                                                                                                                                                                                                    | Destination    |

|-------------------------------------------------------------------------------------------------------------|-----------------------------------------------------------------------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------------|

| X/INT-CI<br>X/INT-EVENT<br>DT/XR<br>HOLD<br>X/HOLDAOUT<br>XENBUF<br>XREQRDY<br>TxD<br>RTS<br>AB196<br>DIA90 | 1<br>1<br>1<br>1<br>1<br>1<br>1<br>1<br>1<br>1<br>1<br>1<br>1<br>1<br>1<br>1<br>1 | Interrupt Confirmation/Indication<br>Interrupt Event Register<br>Data Transmit Receive<br>HOLD Request, Tristate Output<br>Hold Acknowledge Out<br>Enable of ext. buffers at X/REQ<br>Ready for ext. bus master<br>Serial send channel<br>Request to Send<br>Address Bus<br>Diagnostic Port |                |

| XCLK2                                                                                                       | 1                                                                                 | 24MHz Clock                                                                                                                                                                                                                                                                                 | System Support |

| хнток                                                                                                       | 1                                                                                 | Hold Token Indication                                                                                                                                                                                                                                                                       | Led            |

Table 1.10-2: Output Pins of the ASPC2

# **SIEMENS**

25 Bidirectional Signals:

| Signal<br>Name                        | Quantity               | Function                                                     | Source/Destination                                                                                   |

|---------------------------------------|------------------------|--------------------------------------------------------------|------------------------------------------------------------------------------------------------------|

| AB50<br>DB150*<br>XBHE*<br>XRD<br>XWR | 6<br>16<br>1<br>1<br>1 | Address Bus<br>Data Bus<br>Byte High Enable<br>Read<br>Write | CPU, Memory, Sys. Support<br>CPU, Memory<br>CPU, Memory<br>CPU, Memory<br>CPU, Memory<br>CPU, Memory |

\* TTL input with integrated pull-up

### Table 1.10-3: Bidirectional Pins of the ASPC2

| Other Signals | : | VDD Pins<br>VSS Pins<br>Test Pins           | 10<br>17<br>2        |

|---------------|---|---------------------------------------------|----------------------|

| Total:        |   | Inputs:<br>Outputs:<br>Bidirect.:<br>Other: | 11<br>35<br>25<br>29 |

|               | - | All Pins:                                   | 100                  |

## 1.10 Pin Assignment

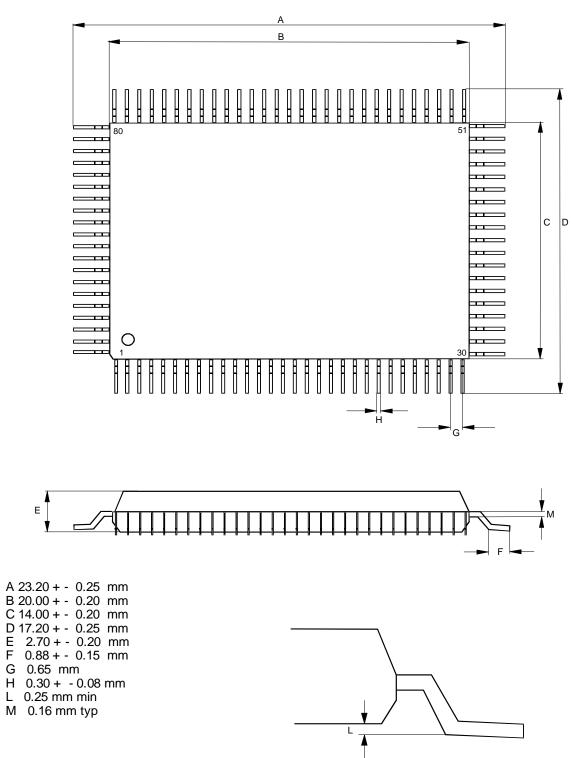

The ASPC2 has a 100 pin P-MQFP EIAJ case:

| 01: XRD        | Т   | 26: XREQ      | Т   | 51: AB11  |    | 76: DIA5     |     |

|----------------|-----|---------------|-----|-----------|----|--------------|-----|

|                | 1   |               | 1   |           |    |              |     |

| 02: DT/XR      |     | 27: XREQRDY   |     | 52: AB10  |    | 77: VSS      |     |

| 03: VSS2       |     | 28: XENBUF    |     | 53: VSS   |    | 78: DIA4     |     |

| 04: VDD3       |     | 29: VSS2      |     | 54: VDD3  |    | 79: DIA3     |     |

| 05: XBHE/XWRH  | TPU | 30: XINT/MOT  | CPD | 55: AB9   |    | 80: VSS2     |     |

| 06: HOLD       |     | 31: XTEST0    | С   | 56: AB8   |    | 81: DIA2     |     |

| 07: DB7        | TPU | 32: XTEST1    | С   | 57: AB7   |    | 82: DIA1     |     |

| 08: DB6        | TPU | 33: XWRL_MODE | CPU | 58: AB6   |    | 83: DIA0     |     |

| 09: VDD        |     | 34: XCTS      | С   | 59: VDD   |    | 84: X/INT-EV |     |

| 10: VSS        |     | 35: DIA9      |     | 60: VSS   |    | 85: X/INT-CI |     |

| 11: DB5        | TPU | 36: XB8/B16   | CPU | 61: AB5   | Т  | 86: RTS      |     |

| 12: DB4        | TPU | 37: XWR/XWRL  | Т   | 62: AB4   | Т  | 87: TXD      |     |

| 13: DB3        | TPU | 38: AB19      |     | 63: AB3   | Т  | 88: DB15     | TPU |

| 14: DB2        | TPU | 39: AB18      |     | 64: AB2   | Т  | 89: DB14     | TPU |

| 15: VDD        |     | 40: VDD       |     | 65: VDD   |    | 90: VDD      |     |

| 16: VSS        |     | 41: VSS       |     | 66: VSS   |    | 91: VSS      |     |

| 17: VSS3       |     | 42: AB17      |     | 67: VSS3  |    | 92: VSS3     |     |

| 18: DB1        | TPU | 43: AB16      |     | 68: AB1   | Т  | 93: DB13     | TPU |

| 19: DB0        | TPU | 44: AB15      |     | 69: AB0   | Т  | 94: DB12     | TPU |

| 20: X/HOLDAOUT |     | 45: AB14      |     | 70: XCLK2 |    | 95: DB11     | TPU |

| 21: X/HOLDAIN  | Т   | 46: VSS       |     | 71: CLK   | CS | 96: DB10     | TPU |

| 22: RESET      | CS  | 47: VDD       |     | 72: XHTOK |    | 97: VSS      |     |

| 23: RXD        | С   | 48: VSS2      |     | 73: DIA8  |    | 98: VDD      |     |

| 24: XRDY       | Т   | 49: AB13      |     | 74: DIA7  |    | 99: DB9      | TPU |

| 25: XCS        | Т   | 50: AB12      |     | 75: DIA6  |    | 100: DB8     | TPU |

Table 1.11-1: Pin Assignment

VDD: Output pads and internals cells

- VDD3: Input pads

- VSS: Output pads

- VSS2: Internal cells

- VSS3: Input pads

- T: TTL level

- TPU: TTL level with pull-up

- C: CMOS input

- CPU: CMOS input with pull-up

- CPD: CMOS input with pull down

- CS: CMOS Schmitt Trigger input

## 1.11 Housing (P-MQFP100)

P-MOFP100 Case

Figure 1.12-1: Mechanics

## 1.12 Notes on Processing

Always, EGB protective steps have to be taken regarding all electronic components.

The ASPC2 is a **cracking sensitive device** that has to be handled accordingly.

## 2 FLC Interface

## 2.1 System Control Block

The system control block SCB (refer to Figure 2.1.1-1) is the interface between the ASPC2 and the FLC.

The following lists are chained in the SCB:

- Background Message High List (BMH)

- Background Message Low List (BML)

- Confirmation Indication High List (CON-IND-HIGH) or separate Indication High List (IND-SEP-HIGH)

- Confirmation Indication Low List (CON-IND-LOW) or separate Indication Low List (IND-SEP-LOW)

- Separate Confirmation High List (CON-SEP-HIGH)

- Separate Confirmation Low List (CON-SEP-LOW)

- O NOT-OKAY High List (NOT-OK-HIGH)

- O NOT-OKAY Low List (NOT-OK-LOW)

- O DEFAULT SAP List, SAP Lists (SAP[0..63])

Each request is entered in an application block (REQ APB) (refer to Chapter 2.2.1). Several such REQ APBs together make up a chained list, also called queue (refer to Chapter 2.3.1).

#### 2.1.1 Request Lists (BMH, BML)

The ASPC2 manages the following background message lists (BMH, BML) in which the FLC enters send requests. The ASPC2 processes the BMH list (high priority) and the BML list (low priority). For each new request selection, the ASPC2 always goes first to the list with the highest priority; if it is empty, it branches to the next, lower priority etc.. Regardless of the token holding time, at least one high priority request is processed per token rotation. The two request priorities of PROFIBUS are mapped onto the background lists BMH and BML.

All high priority requests are confirmed in a high priority confirmation list (CON-IND-/CON-SEP-/NOT-OK-HIGH), and all low priority requests in a low priority confirmatrion list (CON-IND-/CON-SEP-/ NOT-OK-LOW) (see below). The priority is not determined from the entry in the corresponding request lists, but from the coding of the PRIO bit in Opcode 7..0 of the application block (refer to Chapter 2.3.1). The GAP messages are attached only to the BML.

| Reserved                       | next-blk-ptr<br>prev-blk-ptr                                                                                                                                                                          |

|--------------------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| H<br>➡Reserved                 | next-blk-ptr<br>prev-blk-ptr                                                                                                                                                                          |

| H<br>BM-HIGH                   | next-blk-ptr<br>prev-blk-ptr                                                                                                                                                                          |

| BM-LOW                         | next-blk-ptr<br>prev-blk-ptr                                                                                                                                                                          |

| H<br>CON-IND-HIG               |                                                                                                                                                                                                       |

| H<br>CON-IND-LO<br>(IND-SEP-LC |                                                                                                                                                                                                       |

| H<br>(CON-SEP-H                | IGH) next-blk-ptr<br>prev-blk-ptr                                                                                                                                                                     |

| ICON-SEP-L                     | OW) next-blk-ptr                                                                                                                                                                                      |

| ⊣<br>(NOT-OK-HI0               | GH) next-blk-ptr<br>prev-blk-ptr                                                                                                                                                                      |

| (NOT-OK-LO                     | W) next-blk-ptr<br>prev-blk-ptr                                                                                                                                                                       |

|                                | Master-Watchdog                                                                                                                                                                                       |

| H<br>Reserved                  |                                                                                                                                                                                                       |

|                                |                                                                                                                                                                                                       |

| DEFAULT-S                      | AP ind-next-blk-ptr<br>ind-prev-blk-ptr<br>rup-next-blk-ptr<br>rup-prev-blk-ptr                                                                                                                       |

|                                | req-buf-length         (0 bis 246)           req-sa         (All-1; 01111111; 0xxxxxxx; 1xxxxxxx)           req-ssap         (All-1; 00xxxxx)           req-fc         (SAP-Lock,RS/UE,RR,All-2/xxxx) |

| SAP 0 - 63                     | ind-next-blk-ptr<br>ind-prev-blk-ptr<br>rup-next-blk-ptr<br>rup-prev-blk-ptr                                                                                                                          |

|                                | req-buf-length (0 bis 244)<br>req-sa (All-1; 01111111; 0xxxxxxx; 1xxxxxx)<br>req-ssap (All-1; 00xxxxx)<br>req-fc (SAP-Lock,RS/UE,RR,All-2/xxxx)                                                       |

All-1 = 11111111; All-2 = xxxx0000;

Figure 2.1.1-1: SCB of the ASPC2

The ASPC2 now processes successively the REQ APBs from the request lists. It fetches the request message from the request segment of the application block, and sends it to the remote station. If the response is faultless, it enters -if needed- the response data and the status in the response segment of the application block. If the remote station does not respond, or if its response was received faulty, the ASPC2 generates a repetition if needed, etc. If the last repetition is unsuccessful also, the request will be confirmed with 'NA (No Access)'.

If "SEP LIST = 0" (Mode Register 0), the ASPC2 removes a request that was processed (REQ APB) from the corresponding request list and enters it in the CON IND HIGH or CON IND LOW (refer to Chapter 2.3.1). In addition, it generates an interrupt for the FLC for the executed **confirmation (INT CI)**. If "SEP LIST = 1" is set, the ASPC2 enters the faultless send requests in the CON SEP HIGH/LOW, and the faulty requests (for example "NA") in the NOT OK HIGH/LOW with the associated **event interrupts (INT EV) CON SEP LIST** or **NOT OK LIST** (refer to Chapter

#### 4.3).

If the respective request lists are empty, the ASPC2 sets "REQ EMPTY = 1" in Mode Register 1. It now does not access the request lists until the FLC has chained a new REQ APB in the lists. Each time the FLC chaines an REQ APB in the request lists, it has to set "REQ EMPTY = 0" in Mode Register 1. All request lists can be locked at the ASPC2. If "LOCK REQUEST = 1" is set in Mode Register 1, no requests will be sent. The ASPC2 immediately passes the token.

The SCB is only an anchor for the BMH and BML. The '**next block pointer (next blk ptr)** points to the first REQ APB of the list (refer to Chapter 2.3.1). If there is no REQ APB in the list, the 'next blk ptr' points to itself.

#### Watchdog for Master Monitoring

A watchdog function is located on the 28.H word of the SCB which monitors the master. When a new request is executed, the ASPC2 decrements this cell. When the value '0000H' is reached, no more requests are processed, and "REQ EMPTY = 1" is set. In this case, however, the counter stops in the SCB on '0001H'. The user has to load this cell cyclically to a start value, which has to be < 'FF7FH', however. If the value is higher (>= 'FF7FH'), the watchdog is turned off.

#### 2.1.2 CON IND HIGH, CON IND LOW or IND SEP HIGH, IND SEP LOW

If "SEP LIST = 0", all processed applications blocks get into the confirmation-indication lists, the high prioity APBs in the CON IND HIGH, and the low priority APBs in the CON IND LOW. REQ APBs from the request lists are entered as **confirmation**, and IND APBs and RUP APBs from the SAP lists (refer to Chapter 2.1.5) as **indicaton** (refer to Chapter 2.2.1). Each entry is signalled to the FLC with an interrupt (**INT CI**) (refer to Chapter 4.3).

In the mode "SEP LIST = 1", these lists represent pure indication lists. Here, the ASPC2 enters only the processed IND APBs and RUP APBs of the SAP lists. Each entry is signalled to the FLC by interrupt (**INT CI**).

Here also, the SCB is used only as an anchor for CON IND HIGH/LOW or IND SEP HIGH/LOW. The 'next blk ptr' points to the first APB in the list. If there is no APB in the list, it points to itself.

#### 2.1.3 CON SEP HIGH, CON SEP LOW

These lists have a meaning only for "SEP LIST = 1" or collect requests. If "SEP LIST = 1", all faultlessly executed send requests are entered in these lists (confirmation); that is, all REQ APBs that were acknowledged positive by the remote station, or the blocks that don't require acknowledgement (SDN). Each entry is signalled to the FLC with the event interrupt **CON SEP LIST** (refer to Chapter 4.3). In the case of **collect request**, marked in the opcode field of the REQ APB (refer to Chapter 2.2.1), all send requests associated with the collect service are entered in the CON SEP HIGH/LOW. Here also, the SCB is used only as an anchor for CON SEP HIGH/I OW.

Here also, the SCB is used only as an anchor for CON SEP HIGH/LOW. The 'next blk ptr' points to the first REQ APB in the list. If there is no REQ APB in the list, it points to itself.

#### 2.1.4 NOT OK HIGH, NOT OK LOW

These lists have only one meaning in the case of "SEP LIST = 1" and repeat requests. All request blocks that the remote station acknowledges negative or not at all are stored in these lists by the ASPC2 (refer to Chapter 2.2.1). Each entry is signalled to the FLC with the event interrupt **NOT OK LIST** (refer to Chapter 4.3).

Here also, the SCB is used only as an anchor for NOT OK HIGH/LOW. The 'next blk ptr' points to the first REQ APB in the list. If there is no REQ APB in the list, it points to itself.

#### 2.1.5 SAP Lists (SM SAP, DEFAULT SAP, SAP [0..63])

In the FLC, a data transmission service is processed via a **service access point (SAP)**. If "FULL SAP = 0", there are up to 64 SAPs **SAP [0..63]** at each station at the same time (refer to Mode Register 0). For reasons of message efficiency, the transmission of SAPs can be omitted; then, the data transmission services have to be processed via the **default SAP**. The stations can communicate with each other via any SAP.

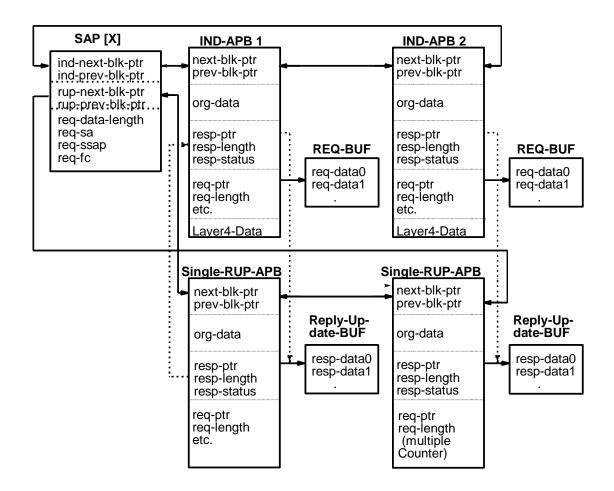

Each service access point (DEFAULT SAP, SAP [0..63] has two separate lists where the FLC makes receive resources (indication application blocks, IND APBs) available in the one list, and reply update application blocks (RUP APBs) in the other (refer to Figure 2.1.5-1). The ASPC2 enters the receive messages in the IND APB list, and fetches the response data from the RUP APB list.

Figure 2.1.5-1: SAP Structure ASPC2

In the RUP APB list, for example, several single reply update buffers can be chained one after the other via one Single RUP APB respectively.

If the ASPC2 receives a request message, first "MAC Lock Flag = 1" under "Type = indication" is set in the first IND APB of the list (refer to Table 2.1.5-1). In addition, "resp length, resp status = 0" is loaded. If there is a reply update buffer at an SRD, the ASPC2 sets "MAC Locked = 1" and "Type = Indication" in the opcode field of the first RUP APB of the list. Then, the request message is transferred to the IND APB, and the reply update buffer is transmitted. If there is no RUP APB, it responds with 'SC' after the request message was cleared. If a reply update buffer was transmitted, the ASPC2 copies, in the case of a valid indication (after the faultless receipt of a new call message header), 'resp ptr', resp length, and resp status' from the RUP APB to the IND APB. In the case of a single RUP APB, "MAC Locked = 0", "Inv.Indication Flag = 0" is then set in the opcode, and the block is entered in the CON IND list (according to the priority of the request message). Then, "MAC Locked = 0", "Inv.Indication Flag = 0", "Reply Flag/Indication Mode Data = 0" is set in the opcode of the IND APB, the PRIO bit is assigned according to the request priority, the block is chained in the CON IND list, and the CON IND interrupt is triggered. In the case of an indication, the difference between a RUP APB and an IND APB in the opcode (Bit(3), can be recognized. In the case of a RUP APB, the ASPC2 does not reset this flag (reply flag). However, the FLC had to set "Reply Flag = 1" when making it available. In the case of the IND APB, the ASPC2 clears this bit position (indication mode data flag).

|                                    | IND-APB<br>Opcode = Opcode | Single RUP-APB<br>Opcode = Opcode |

|------------------------------------|----------------------------|-----------------------------------|

| MAC-Locked set<br>(Receive)        | or 82H                     | or 82H                            |

| MAC-Locked reset (Indication)      |                            |                                   |

| Ind.                               | and 66H<br>(or PRIO-High)  | and 6FH<br>(no PRIO)              |

| Ind. invalid<br>(Inv.Ind.Flag = 0) | and 7CH<br>(stays in SAP)  | and 7DH<br>(stays in SAP)         |

| Ind. invalid<br>(Inv.Ind.Flag = 1) | and 76H<br>(after CON-IND) | and 7FH<br>(after CON-IND)        |

#### Table 2.1.5-1: Opcode Handling

SIEMENS

If the indication is invalid, the ASPC2 sets "MAC Locked = 0" and "Type = 00B" in the opcode of both application blocks if "Inv.Indication Flag = 0", whereby the blocks remain chained in the SAP list. If "Inv.Indication Flag =1" is set, "MAC Locked = 0" is set in both blocks; at the IND APB "Reply Flag/Indication Mode Data = 0" is set; then, first the RUP APB and after that the IND APB, or an APB of either is chained in the low priority CON IND list, and the CON IND interrupt is generated.

So that not all SAP lists have to be set up in the SCB, the highest SAP list number is parameterized for the ASPC2 (SAP MAX, refer to Chapter 4.2.1). If the ASPC2 receives a message to an SAP that is not available, it responds with *No Service Activated* (SD1 response). In each SAP list, the FLC can store validation data about the following:

- Request buffer length (req-buf-length)

- Request station (req-sa)

- Request service access point (req-ssap)

- Request service (req-fc)

This data is valid for all receive messages to the respective SAP. Thus, among other things, private connections can be implemented between 2 stations. If not only certain request stations, request SAPs, and request transmission services are to be allowed, the FLC has to enter the coding "all" in the corresponding fields.

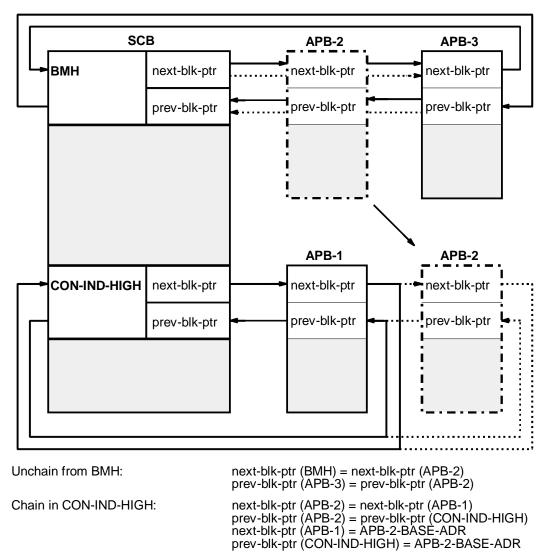

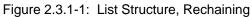

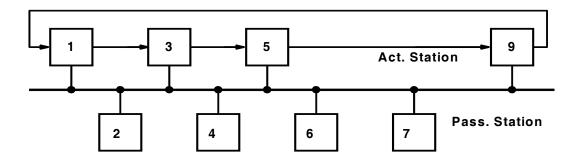

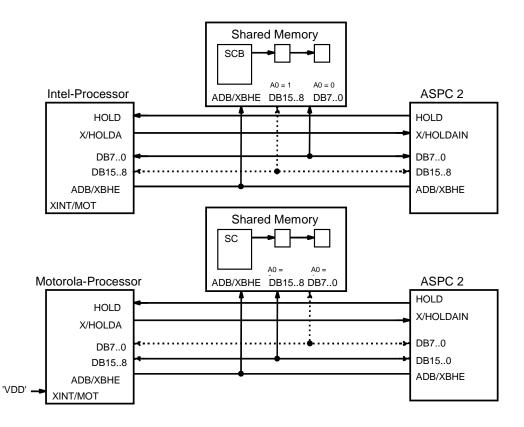

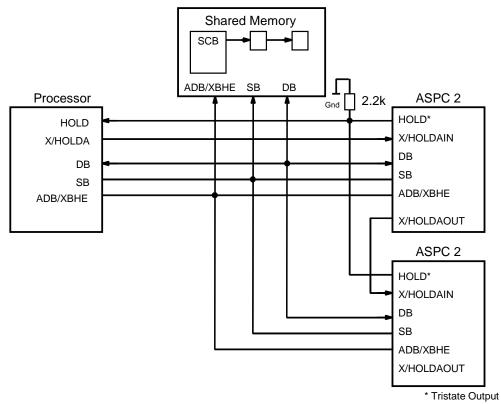

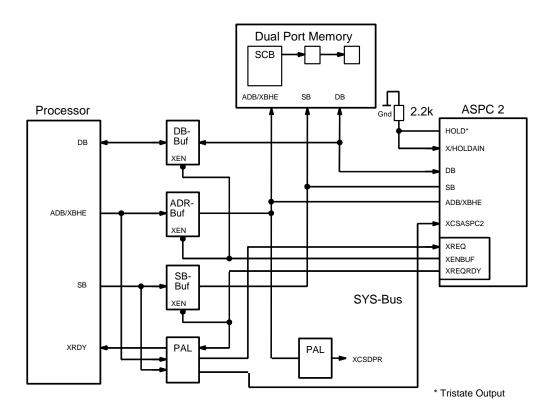

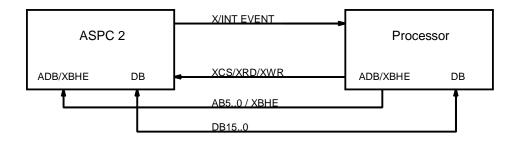

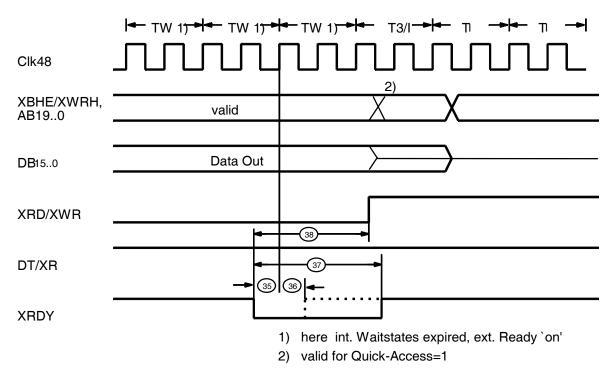

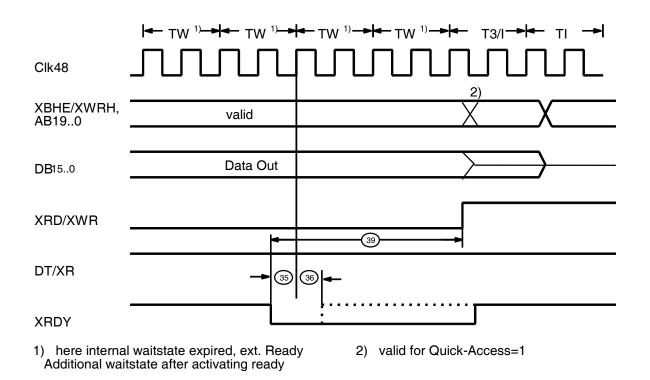

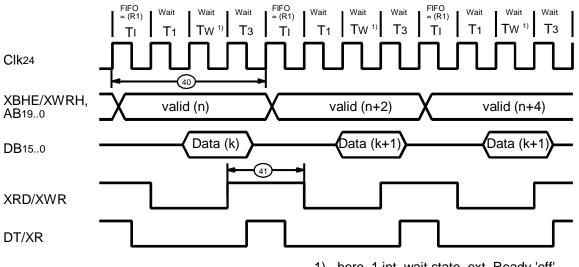

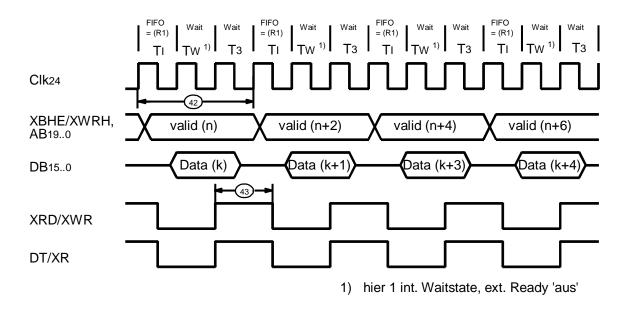

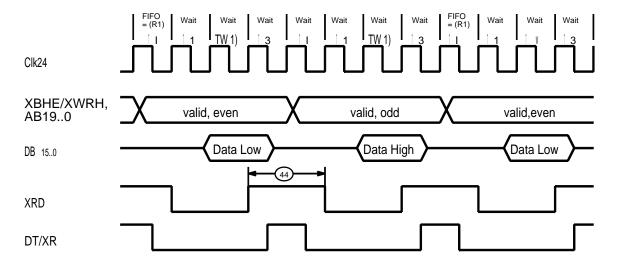

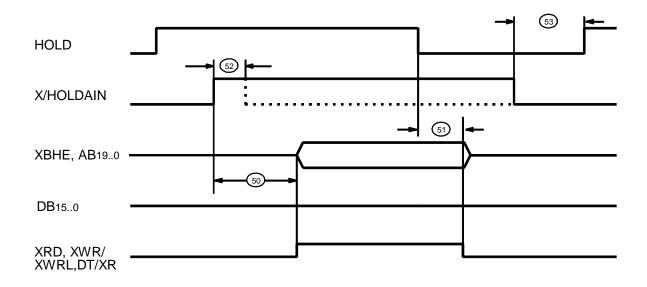

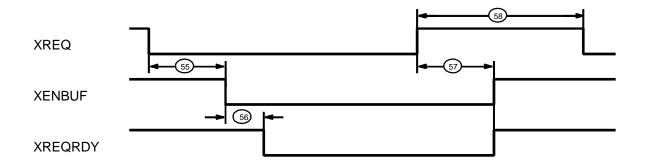

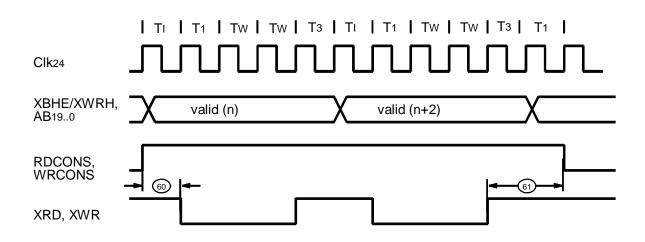

When receiving a request message (call), the ASPC2 validates the corresponding message header characters with the values assigned to it from the SAP list. The following responses are possible: