#### EL5174, EL5374

550MHz Differential Twisted-Pair Drivers

FN7313 Rev 9.00 August 12, 2015

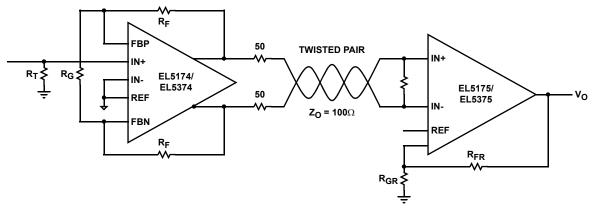

The EL5174 and EL5374 are single and triple high bandwidth amplifiers with an output in differential form. They are primarily targeted for applications such as driving twisted-pair lines in component video applications. The inputs can be in either single-ended or differential form but the outputs are always in differential form.

On the EL5174 and EL5374, two feedback inputs provide the user with the ability to set the gain of each device (stable at minimum gain of one). For a fixed gain of two, please see the EL5173, EL5373 data sheet (FN7312).

The output common mode level for each channel is set by the associated REF pin, which has a -3dB bandwidth of over 110MHz. Generally, these pins are grounded but can be tied to any voltage reference.

All outputs are short circuit protected to withstand temporary overload condition.

The EL5174 is available in a 8 Ld SOIC package and the EL5374 is available in a 28 Ld QSOP package. All are specified for operation over the full -40  $^{\circ}$ C to +85  $^{\circ}$ C temperature range.

#### **Features**

- · Fully differential inputs, outputs, and feedback

- Differential input range ±2.3V

- · 550MHz 3dB bandwidth

- 1100V/µs slew rate

- Low distortion at 5MHz

- Single 5V or dual ±5V supplies

- 60mA maximum output current

- · Low power 12.5mA per channel

- · Pb-free (RoHS compliant)

#### **Applications**

- · Twisted-pair driver

- · Differential line driver

- · VGA over twisted-pair

- · ADSL/HDSL driver

- · Single-ended to differential amplification

- · Transmission of analog signals in a noisy environment

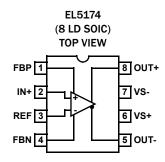

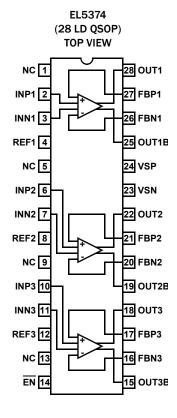

#### **Pinouts**

## **Pin Descriptions**

| EL5174 | EL5374      | PIN NAME            | PIN FUNCTION                                                        |

|--------|-------------|---------------------|---------------------------------------------------------------------|

| 1      |             | FBP                 | Feedback from non-inverting output                                  |

| 2      |             | IN+                 | Non-inverting input                                                 |

| 3      |             | REF                 | Inverting inputs, note that on EL5174, this pin is also the REF pin |

| 4      |             | FBN                 | Feedback from inverting output                                      |

| 5      |             | OUT-                | Inverting output                                                    |

| 6      |             | VS+                 | Positive supply                                                     |

| 7      |             | VS-                 | Negative supply                                                     |

| 8      |             | OUT+                | Non-inverting output                                                |

|        | 17, 21, 27  | FBP3, FBP2, FBP1    | Feedback from non-inverting outputs                                 |

|        | 2, 6, 10    | INP1, INP2, INP3    | Non-inverting inputs                                                |

|        | 3, 7, 11    | INN1, INN2, INN3    | Inverting inputs, note that on EL5174, this pin is also the REF pin |

|        | 16, 20, 26  | FBN3, FBN2, FBN1    | Feedback from inverting outputs                                     |

|        | 15, 19, 25  | OUT3B, OUT2B, OUT1B | Inverting outputs                                                   |

|        | 24          | VSP                 | Positive supply                                                     |

|        | 23          | VSN                 | Negative supply                                                     |

|        | 18, 22, 28  | OUT3, OUT2, OUT1    | Non-inverting outputs                                               |

|        | 1, 5, 9, 13 | NC                  | No connect; grounded for best crosstalk performance                 |

|        | 4, 8, 12    | REF1, REF2, REF3    | Reference inputs, sets common-mode output voltage                   |

|        | 14          | EN                  | ENABLE                                                              |

## **Ordering Information**

| PART NUMBER<br>(Notes 1, 2, 3)                                               | PART<br>MARKING | TEMP. RANGE<br>(°C) | PACKAGE<br>(RoHS Compliant) | PKG.<br>DWG. # |

|------------------------------------------------------------------------------|-----------------|---------------------|-----------------------------|----------------|

| EL5174ISZ                                                                    | 5174ISZ         | -40 to +85          | 8 Ld SOIC                   | M8.15E         |

| EL5374IUZ<br>(No longer available,<br>recommended replacement:<br>EL5373IUZ) | EL5374IUZ       | -40 to +85          | 28 Ld QSOP                  | M28.15         |

#### NOTE:

- 1. Add "-T\*" suffix for tape and reel. Please refer to TB347 for details on reel specifications.

- 2. These Intersil Pb-free plastic packaged products employ special Pb-free material sets, molding compounds/die attach materials, and 100% matte tin plate plus anneal (e3 termination finish, which is RoHS compliant and compatible with both SnPb and Pb-free soldering operations). Intersil Pb-free products are MSL classified at Pb-free peak reflow temperatures that meet or exceed the Pb-free requirements of IPC/JEDEC J STD-020.

- 3. For Moisture Sensitivity Level (MSL), please see device information page for <u>EL5174</u>, <u>EL5374</u>. For more information on MSL please see tech brief <u>TB363</u>.

### Absolute Maximum Ratings (T<sub>A</sub> = +25°C)

| Supply Voltage (V <sub>S</sub> + to V <sub>S</sub> -)          |                                        |

|----------------------------------------------------------------|----------------------------------------|

| Supply Voltage Rate-of-rise (dV/dT)                            | <b>1</b> V/μs                          |

| Input Voltage (IN+, IN- to V <sub>S</sub> +, V <sub>S</sub> -) | $V_{S^{-}}$ - 0.3V to $V_{S}$ + + 0.3V |

| Differential Input Voltage (IN+ to IN-)                        | ±4.8V                                  |

| Maximum Output Current                                         | ±60mA                                  |

#### **Thermal Information**

| Thermal Resistance (Typical, Note 4)             | $\theta_{JA}(^{\circ}C/W)$ |

|--------------------------------------------------|----------------------------|

| 8 Ld SOIC Package                                | 120.40                     |

| 28 Ld QSOP Package                               |                            |

| Operating Junction Temperature                   | +135°C                     |

| Ambient Operating Temperature                    | 40°C to +85°C              |

| Storage Temperature Range6                       | 5°C to +150°C              |

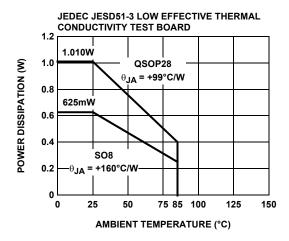

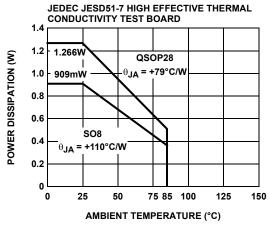

| Power Dissipation                                | See Curves                 |

| Pb-Free Reflow Profile                           | . see link below           |

| http://www.intersil.com/pbfree/Pb-FreeReflow.asp |                            |

CAUTION: Do not operate at or near the maximum ratings listed for extended periods of time. Exposure to such conditions may adversely impact product reliability and result in failures not covered by warranty.

#### NOTE

4. θ<sub>JA</sub> is measured with the component mounted on a high effective thermal conductivity test board in free air. See Tech Brief TB379 for details.

IMPORTANT NOTE: All parameters having Min/Max specifications are guaranteed. Typ values are for information purposes only. Unless otherwise noted, all tests are at the specified temperature and are pulsed tests, therefore:  $T_J = T_C = T_A$

## **Electrical Specifications** $V_S+=+5V$ , $V_{S^-}=-5V$ , $T_A=+25\,^{\circ}C$ , $V_{IN}=0V$ , $R_{LD}=1$ k $\Omega$ , $R_F=0$ , $R_G=0$ PEN, $C_{LD}=2.7$ pF, unless otherwise specified.

| PARAMETER                  | DESCRIPTION                                               | CONDITIONS                                        | MIN<br>(Note 5) | TYP  | MAX<br>(Note 5) | UNIT   |

|----------------------------|-----------------------------------------------------------|---------------------------------------------------|-----------------|------|-----------------|--------|

| AC PERFORMAI               | NCE                                                       | -                                                 |                 |      |                 |        |

| BW                         | -3dB Bandwidth                                            | $A_V = 1$ , $C_{LD} = 2.7 pF$                     |                 | 550  |                 | MHz    |

|                            |                                                           | $A_V = 2$ , $R_F = 500$ , $C_{LD} = 2.7pF$        |                 | 130  |                 | MHz    |

|                            |                                                           | $A_V = 10, R_F = 500, C_{LD} = 2.7pF$             |                 | 20   |                 | MHz    |

| BW                         | ±0.1dB Bandwidth                                          | A <sub>V</sub> = 1, C <sub>LD</sub> = 2.7pF       |                 | 120  |                 | MHz    |

| SR                         | Slew Rate (EL5174)                                        | V <sub>OUT</sub> = 3V <sub>P-P</sub> , 20% to 80% | 800             | 1100 |                 | V/µs   |

|                            | Slew Rate (EL5374)                                        | V <sub>OUT</sub> = 3V <sub>P-P</sub> , 20% to 80% | 600             | 850  |                 | V/µs   |

| t <sub>STL</sub>           | Settling Time to 0.1%                                     | V <sub>OUT</sub> = 2V <sub>P-P</sub>              |                 | 10   |                 | ns     |

| tovr                       | Output Overdrive Recovery Time                            |                                                   |                 | 20   |                 | ns     |

| GBWP                       | Gain Bandwidth Product                                    |                                                   |                 | 200  |                 | MHz    |

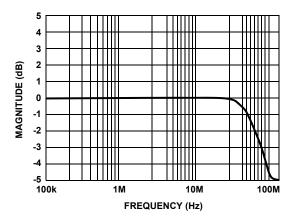

| V <sub>REF</sub> BW (-3dB) | V <sub>REF</sub> -3dB Bandwidth                           | A <sub>V</sub> = 1, C <sub>LD</sub> = 2.7pF       |                 | 110  |                 | MHz    |

| V <sub>REF</sub> SR+       | V <sub>REF</sub> Slew Rate - Rise                         | V <sub>OUT</sub> = 2V <sub>P-P</sub> , 20% to 80% |                 | 134  |                 | V/µs   |

| V <sub>REF</sub> SR-       | V <sub>REF</sub> Slew Rate - Fall                         | V <sub>OUT</sub> = 2V <sub>P-P</sub> , 20% to 80% |                 | 70   |                 | V/µs   |

| $V_N$                      | Input Voltage Noise                                       | at 10kHz                                          |                 | 21   |                 | nV/√Hz |

| I <sub>N</sub>             | Input Current Noise                                       | at 10kHz                                          |                 | 2.7  |                 | pA/√Hz |

| HD2                        | Second Harmonic Distortion                                | V <sub>OUT</sub> = 2V <sub>P-P</sub> , 5MHz       |                 | -95  |                 | dBc    |

|                            |                                                           | $V_{OUT} = 2V_{P-P}$ , 20MHz                      |                 | -94  |                 | dBc    |

| HD3                        | Third Harmonic Distortion                                 | V <sub>OUT</sub> = 2V <sub>P-P</sub> , 5MHz       |                 | -88  |                 | dBc    |

|                            |                                                           | $V_{OUT} = 2V_{P-P}$ , 20MHz                      |                 | -87  |                 | dBc    |

| dG                         | Differential Gain at 3.58MHz                              | R <sub>LD</sub> = 300Ω, A <sub>V</sub> = 2        |                 | 0.06 |                 | %      |

| dθ                         | Differential Phase at 3.58MHz                             | R <sub>LD</sub> = 300Ω, A <sub>V</sub> = 2        |                 | 0.13 |                 | 0      |

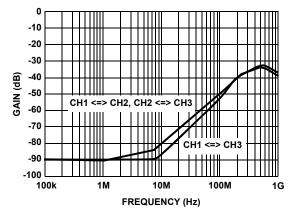

| e <sub>S</sub>             | Channel Separation - for EL5374 only                      | at f = 1MHz                                       |                 | 90   |                 | dB     |

| INPUT CHARAC               | TERISTICS                                                 |                                                   | -               |      |                 |        |

| V <sub>OS</sub>            | Input Referred Offset Voltage                             | (EL5174)                                          |                 | ±1.4 | ±25             | mV     |

|                            |                                                           | (EL5374)                                          |                 | ±2.2 | ±25             | m۷     |

| I <sub>IN</sub>            | Input Bias Current (V <sub>IN</sub> +, V <sub>IN</sub> -) |                                                   | -30             | -14  | -7              | μΑ     |

| I <sub>REF</sub>           | Input Bias Current (V <sub>REF</sub> )                    |                                                   | 0.5             | 2.3  | 4               | μΑ     |

| R <sub>IN</sub>            | Differential Input Resistance                             |                                                   |                 | 150  |                 | kΩ     |

## **Electrical Specifications** $V_S^+ = +5V$ , $V_{S^-} = -5V$ , $T_A = +25 \,^{\circ}$ C, $V_{IN} = 0V$ , $R_{LD} = 1 \,\mathrm{k}\Omega$ , $R_F = 0$ , $R_G = 0 \,\mathrm{PEN}$ , $C_{LD} = 2.7 \,\mathrm{pF}$ , unless otherwise specified. (Continued)

| PARAMETER              | DESCRIPTION                                                              | CONDITIONS                            | MIN<br>(Note 5)       | TYP   | MAX<br>(Note 5)       | UNIT               |

|------------------------|--------------------------------------------------------------------------|---------------------------------------|-----------------------|-------|-----------------------|--------------------|

| C <sub>IN</sub>        | Differential Input Capacitance                                           |                                       |                       | 1     |                       | pF                 |

| DMIR                   | Differential Mode Input Range                                            |                                       | ±2.1                  | ±2.3  | ±2.5                  | V                  |

| CMIR+                  | Common Mode Positive Input Range at V <sub>IN</sub> +, V <sub>IN</sub> - |                                       |                       | 3.4   |                       | ٧                  |

| CMIR-                  | Common Mode Negative Input Range at V <sub>IN</sub> +, V <sub>IN</sub> - |                                       |                       | -4.3  |                       | ٧                  |

| V <sub>REFIN</sub> +   | Positive Reference Input Voltage Range (EL5374)                          | $V_{IN} + = V_{IN} - = 0V$            | 3.4                   | 3.7   |                       | ٧                  |

| V <sub>REFIN</sub> -   | Negative Reference Input Voltage Range (EL5374)                          | $V_{IN} + = V_{IN} - = 0V$            |                       | -3.3  | -3                    | ٧                  |

| V <sub>REFOS</sub>     | Output Offset Relative to V <sub>REF</sub> (EL5374)                      |                                       |                       | ±50   | ±100                  | m۷                 |

| CMRR                   | Input Common Mode Rejection Ratio (EL5374)                               | V <sub>IN</sub> = ±2.5V               | 65                    | 78    |                       | dB                 |

| Gain                   | Gain Accuracy                                                            | V <sub>IN</sub> = 1V (EL5174)         | 0.980                 | 0.995 | 1.010                 | ٧                  |

|                        |                                                                          | V <sub>IN</sub> = 1V (EL5374)         | 0.978                 | 0.993 | 1.008                 | V                  |

| OUTPUT CHARA           | CTERISTICS                                                               |                                       |                       |       |                       |                    |

| V <sub>OUT</sub>       | Output Voltage Swing                                                     | $R_L = 500\Omega$ to GND (EL5174)     |                       | ±3.4  |                       | ٧                  |

|                        |                                                                          | $R_L = 500\Omega$ to GND (EL5374)     | ±3.6                  | ±3.8  |                       | ٧                  |

| I <sub>OUT</sub> (Max) | Maximum Output Current                                                   | $R_L = 10\Omega, V_{IN} + = \pm 3.2V$ | ±50                   | ±60   | ±100                  | mA                 |

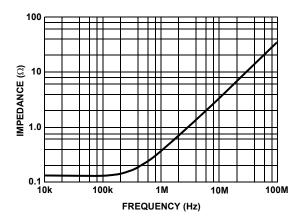

| R <sub>OUT</sub>       | Output Impedance                                                         |                                       |                       | 130   |                       | $\mathbf{m}\Omega$ |

| SUPPLY                 |                                                                          |                                       |                       |       |                       |                    |

| V <sub>SUPPLY</sub>    | Supply Operating Range                                                   | V <sub>S</sub> + to V <sub>S</sub> -  | 4.75                  |       | 11                    | ٧                  |

| I <sub>S(ON)</sub>     | Power Supply Current - Per Channel                                       |                                       | 10                    | 12.5  | 14                    | mA                 |

| I <sub>S(OFF)</sub> +  | Positive Power Supply Current - Disabled (EL5374)                        | EN pin tied to 4.8V                   |                       | 1.7   | 10                    | μΑ                 |

| I <sub>S(OFF)</sub> -  | Negative Power Supply Current - Disabled (EL5374)                        |                                       | -200                  | -120  |                       | μΑ                 |

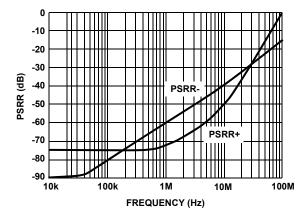

| PSRR                   | Power Supply Rejection Ratio                                             | V <sub>S</sub> from ±4.5V to ±5.5V    | 60                    | 75    |                       | dB                 |

| ENABLE (EL5374         | 1 ONLY)                                                                  |                                       |                       | 1     | 1                     |                    |

| t <sub>EN</sub>        | Enable Time                                                              |                                       |                       | 130   |                       | ns                 |

| t <sub>DS</sub>        | Disable Time                                                             |                                       |                       | 1.2   |                       | μs                 |

| V <sub>IH</sub>        | EN Pin Voltage for Power-Up                                              |                                       |                       |       | V <sub>S</sub> + -1.5 | ٧                  |

| V <sub>IL</sub>        | EN Pin Voltage for Shut-Down                                             |                                       | V <sub>S</sub> + -0.5 |       |                       | ٧                  |

| I <sub>IH-EN</sub>     | EN Pin Input Current High                                                | At V <sub>EN</sub> = 5V               |                       | 123   | 150                   | μΑ                 |

| I <sub>IL-EN</sub>     | EN Pin Input Current Low                                                 | At V <sub>EN</sub> = OV               | -10                   | -8    |                       | μΑ                 |

#### NOTE:

<sup>5.</sup> Parameters with MIN and/or MAX limits are 100% tested at +25°C, unless otherwise specified. Temperature limits established by characterization and are not production tested.

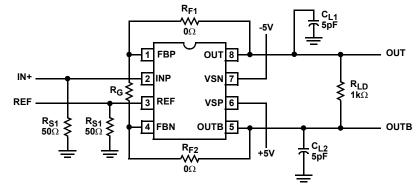

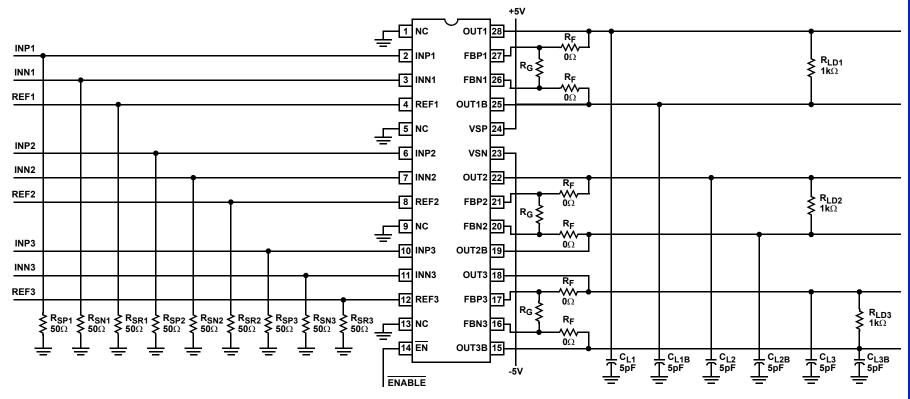

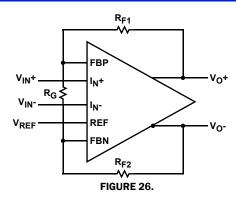

## **Connection Diagrams**

**FIGURE 1. EL5174**

FIGURE 2. EL5374

## **Typical Performance Curves**

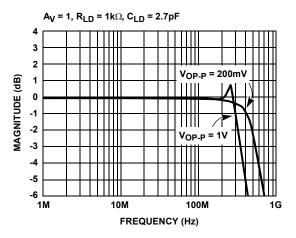

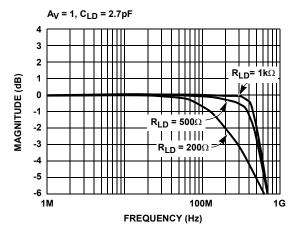

FIGURE 3. FREQUENCY RESPONSE

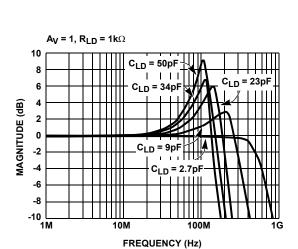

FIGURE 5. FREQUENCY RESPONSE vs C<sub>LD</sub>

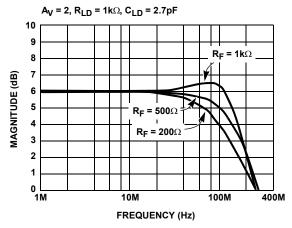

FIGURE 7. FREQUENCY RESPONSE

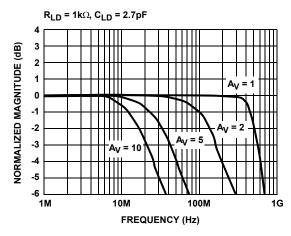

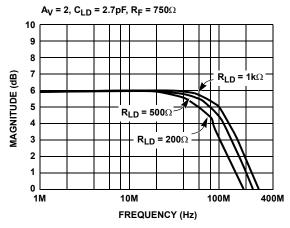

FIGURE 4. FREQUENCY RESPONSE FOR VARIOUS GAIN

FIGURE 6. FREQUENCY RESPONSE vs R<sub>LD</sub>

FIGURE 8. FREQUENCY RESPONSE vs R<sub>LD</sub>

## Typical Performance Curves (Continued)

FIGURE 9. FREQUENCY RESPONSE - VREF

FIGURE 10. PSRR vs FREQUENCY

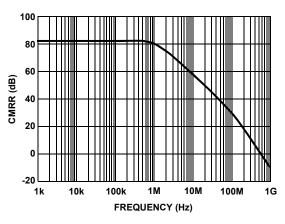

FIGURE 11. CMRR vs FREQUENCY

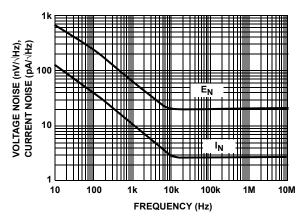

FIGURE 12. VOLTAGE AND CURRENT NOISE vs FREQUENCY

FIGURE 13. CHANNEL ISOLATION (EL5374 ONLY)

FIGURE 14. OUTPUT IMPEDANCE vs FREQUENCY

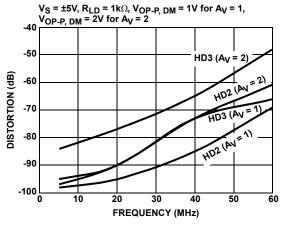

## Typical Performance Curves (Continued)

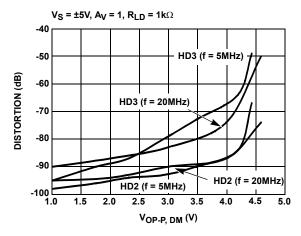

FIGURE 15. HARMONIC DISTORTION vs DIFFERENTIAL OUTPUT VOLTAGE

$V_S = \pm 5V$ ,  $A_V = 2$ ,  $R_{LD} = 1k\Omega$

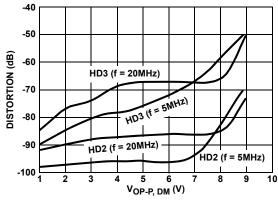

FIGURE 16. HARMONIC DISTORTION vs DIFFERENTIAL OUTPUT VOLTAGE

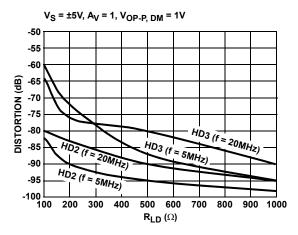

FIGURE 17. HARMONIC DISTORTION vs  $R_{LD}$

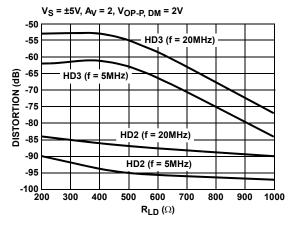

FIGURE 18. HARMONIC DISTORTION vs  $R_{LD}$

FIGURE 19. HARMONIC DISTORTION vs FREQUENCY

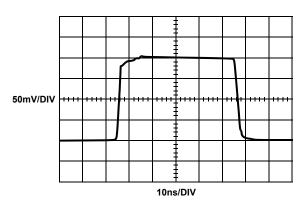

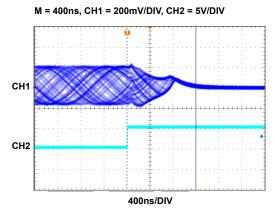

FIGURE 20. SMALL SIGNAL TRANSIENT RESPONSE

## Typical Performance Curves (Continued)

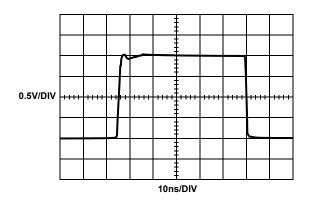

FIGURE 21. LARGE SIGNAL TRANSIENT RESPONSE

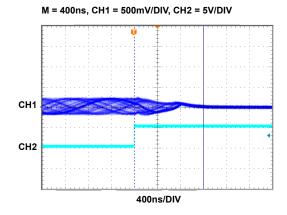

FIGURE 22. ENABLED RESPONSE

FIGURE 23. DISABLED RESPONSE

FIGURE 24. PACKAGE POWER DISSIPATION vs AMBIENT TEMPERATURE

FIGURE 25. PACKAGE POWER DISSIPATION vs AMBIENT TEMPERATURE

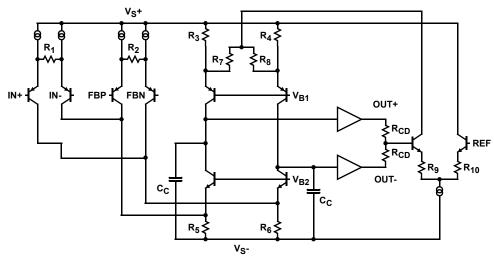

### **Simplified Schematic**

# **Description of Operation and Application Information**

#### **Product Description**

The EL5174 and EL5374 are wide bandwidth, low power and single/differential ended to differential output amplifiers. The EL5174 is a single channel differential amplifier. Since the  $I_{N^-}$  pin and REF pin are tied together internally, the EL5174 can be used as a single-ended to differential converter. The EL5374 is a triple channel differential amplifier. The EL5374 has a separate  $I_{N^-}$  pin and REF pin for each channel. It can be used as single/differential ended to differential converter. The EL5174 and EL5374 are internally compensated for closed loop gain of +1 of greater. Connected in a gain of 1 and driving a  $1 k\Omega$  differential load, the EL5174 and EL5374 have a -3dB bandwidth of 550MHz. Driving a  $200\Omega$  differential load at gain of 2, the bandwidth is about 130MHz. The EL5374 is available with a power-down feature to reduce the power while the amplifier is disabled.

#### **Input, Output and Supply Voltage Range**

The EL5174 and EL5374 have been designed to operate with a single supply voltage of 5V to 10V or split supplies with its total voltage from 5V to 10V. The amplifiers have an input common mode voltage range from -4.3V to 3.4V for ±5V supply. The differential mode input range (DMIR) between the two inputs is from -2.3V to +2.3V. The input voltage range at the REF pin is from -3.3V to 3.7V. If the input common mode or differential mode signal is outside the above-specified ranges, it will cause the output signal to become distorted.

The output of the EL5174 and EL5374 can swing from -3.8V to +3.8V at  $1 \text{k}\Omega$  differential load at  $\pm 5 \text{V}$  supply. As the load resistance becomes lower, the output swing is reduced.

## Differential and Common Mode Gain Settings

For EL5174, since the  $I_{N^-}$  pin and REF pin are bound together as the REF pin in an 8 Ld package, the signal at the REF pin is part of the common mode signal and also part of the

differential mode signal. For the true balance differential outputs, the REF pin must be tied to the same bias level as the I<sub>N</sub>+ pin. For a  $\pm 5$ V supply, just tie the REF pin to GND if the I<sub>N</sub>+ pin is biased at 0V with a  $50\Omega$  or  $75\Omega$  termination resistor. For a single supply application, if the I<sub>N</sub>+ is biased to half of the rail, the REF pin should be biased to half of the rail also.

The gain setting for EL5174 is expressed in Equation 1:

$$\begin{split} &V_{ODM} = V_{IN} + \times \left(1 + \frac{R_{F1} + R_{F2}}{R_G}\right) \\ &V_{ODM} = V_{IN} + = \left(1 + \frac{2R_F}{R_G}\right) \\ &V_{OCM} = V_{RFF} = 0V \end{split} \tag{EQ. 1}$$

Where:

$$V_{RFF} = 0V$$

$$R_{F1} = R_{F2} = R_F$$

The EL5374 has a separate  $I_{N^-}$  pin and REF pin. It can be used as a single/differential ended to differential converter. The voltage applied at REF pin can set the output common mode voltage and the gain is one.

The gain setting for EL5374 is expressed in Equation 2:

$$\begin{split} &V_{ODM} = (V_{IN} + - V_{IN}^{-}) \times \left(1 + \frac{R_{F1} + R_{F2}}{R_{G}}\right) \\ &V_{ODM} = (V_{IN} + - V_{IN}^{-}) \times \left(1 + \frac{2R_{F}}{R_{G}}\right) \end{split} \tag{EQ. 2}$$

$V_{OCM} = V_{REF}$

Where:

$$R_{F1} = R_{F2} = R_{F}$$

## Choice of Feedback Resistor and Gain Bandwidth Product

For applications that require a gain of  $\pm 1$ , no feedback resistor is required. Just short the OUT+ pin to FBP pin and OUT- pin to FBN pin. For gains greater than  $\pm 1$ , the feedback resistor forms a pole with the parasitic capacitance at the inverting input. As this pole becomes smaller, the amplifier's phase margin is reduced. This causes ringing in the time domain and peaking in the frequency domain. Therefore,  $R_F$  has some maximum value that should not be exceeded for optimum performance. If a large value of  $R_F$  must be used, a small capacitor in the few Pico farad range in parallel with  $R_F$  can help to reduce the ringing and peaking at the expense of reducing the bandwidth.

The bandwidth of the EL5174 and EL5374 depends on the load and the feedback network.  $R_F$  and  $R_G$  appear in parallel with the load for gains other than +1. As this combination gets smaller, the bandwidth falls off. Consequently,  $R_F$  also has a minimum value that should not be exceeded for optimum bandwidth performance. For gain of +1,  $R_F$  = 0 is optimum. For the gains other than +1, optimum response is obtained with  $R_F$  between  $500\Omega$  to  $1 k\Omega$ .

The EL5174 and EL5374 have a gain bandwidth product of 200MHz for  $R_{LD} = 1 k\Omega$ . For gains  $\geq$ 5, its bandwidth can be predicted by Equation 3:

$$Gain \times BW = 200MHz$$

(EQ. 3)

#### **Driving Capacitive Loads and Cables**

The EL5174 and EL5374 can drive a 23pF differential capacitor in parallel with  $\text{1k}\Omega$  differential load with less than 5dB of peaking at gain of +1. If less peaking is desired in applications, a small series resistor (usually between  $5\Omega$  to  $50\Omega)$  can be placed in series with each output to eliminate most peaking. However, this will reduce the gain slightly. If the gain setting is greater than 1, the gain resistor  $R_G$  can then be chosen to make up for any gain loss, which may be created by the additional series resistor at the output.

When used as a cable driver, double termination is always recommended for reflection-free performance. For those applications, a back-termination series resistor at the amplifier's output will isolate the amplifier from the cable and allow extensive capacitive drive. However, other applications may have high capacitive loads without a back-termination

resistor. Again, a small series resistor at the output can help to reduce peaking.

#### **Disable/Power-Down (for EL5374 only)**

The EL5374 can be disabled and its outputs placed in a high impedance state. The turn-off time is about 1.2µs and the turn-on time is about 130ns. When disabled, the amplifier's supply current is reduced to 1.7µA for  $I_S+$  and 120µA for  $I_S-$  typically, thereby effectively eliminating the power consumption. The amplifier's power-down can be controlled by standard CMOS signal levels at the EN pin. The applied logic signal is relative to the  $V_S+$  pin. Letting the  $\overline{\text{EN}}$  pin float or applying a signal that is less than 1.5V below  $V_S+$  will enable the amplifier. The amplifier will be disabled when the signal at the  $\overline{\text{EN}}$  pin is above  $V_S+$  - 0.5V.

#### **Output Drive Capability**

The EL5174 and EL5374 have internal short circuit protection. Its typical short circuit current is  $\pm 60$ mA. If the output is shorted indefinitely, the power dissipation could easily increase such that the part will be destroyed. Maximum reliability is maintained if the output current never exceeds  $\pm 60$ mA. This limit is set by the design of the internal metal interconnections.

#### **Power Dissipation**

With the high output drive capability of the EL5174 and EL5374, it is possible to exceed the +135 °C absolute maximum junction temperature under certain load current conditions. Therefore, it is important to calculate the maximum junction temperature for the application to determine if the load conditions or package types need to be modified for the amplifier to remain in the safe operating area.

The maximum power dissipation allowed in a package is determined according to Equation 4:

$$PD_{MAX} = \frac{T_{JMAX} - T_{AMAX}}{\Theta_{JA}}$$

(EQ. 4)

Where:

T<sub>IMAX</sub> = Maximum junction temperature

$T_{AMAX}$  = Maximum ambient temperature

$\theta_{JA}$  = Thermal resistance of the package

The maximum power dissipation actually produced by an IC is the total quiescent supply current times the total power supply voltage, plus the power in the IC due to the load, or as expressed in Equation 5:

$$PD = i \times \left( V_{STOT} \times I_{SMAX} + (V_{STOT} - \Delta V_{O}) \times \frac{\Delta V_{O}}{R_{LD}} \right)$$

(EQ. 5)

Where:

V<sub>STOT</sub> = Total supply voltage = V<sub>S</sub>+ - V<sub>S</sub>-

I<sub>SMAX</sub> = Maximum quiescent supply current per channel

$\Delta V_0$  = Maximum differential output voltage of the application

R<sub>LD</sub> = Differential load resistance

I<sub>LOAD</sub> = Load current

i = Number of channels

By setting the two  $PD_{\mbox{\scriptsize MAX}}$  equations equal to each other, we can solve the output current and R<sub>LD</sub> to avoid the device overheat.

#### **Power Supply Bypassing and Printed Circuit Board Lavout**

As with any high frequency device, a good printed circuit board layout is necessary for optimum performance. Lead lengths should be as short as possible. The power supply pin must be well bypassed to reduce the risk of oscillation. For normal single supply operation, where the  $V_{S^-}$  pin is connected to the ground plane, a single 4.7 $\mu F$  tantalum capacitor in parallel with a 0.1 $\mu F$ ceramic capacitor from V<sub>S</sub>+ to GND will suffice. This same capacitor combination should be placed at each supply pin to ground if split supplies are to be used. In this case, the V<sub>S</sub>- pin becomes the negative supply rail.

For good AC performance, parasitic capacitance should be kept to a minimum. Use of wire-wound resistors should be avoided because of their additional series inductance. Use of sockets should also be avoided if possible. Sockets add parasitic inductance and capacitance that can result in compromised performance. Minimizing parasitic capacitance at the amplifier's inverting input pin is very important. The feedback resistor should be placed very close to the inverting input pin. Strip line design techniques are recommended for the signal traces.

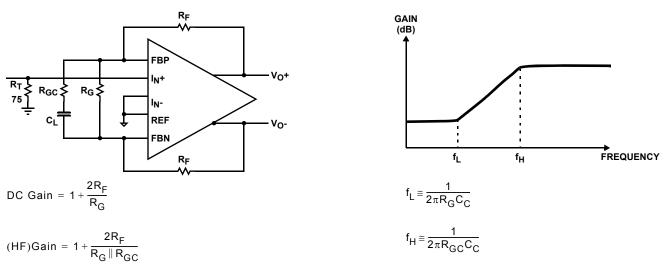

### **Typical Applications**

As the signal is transmitted through a cable, the high frequency signal will be attenuated. One way to compensate this loss is to boost the high frequency gain at the receiver side.

FIGURE 27. TWISTED PAIR CABLE RECEIVER

**FIGURE 28. TRANSMIT EQUALIZER**

### **Revision History**

The revision history provided is for informational purposes only and is believed to be accurate, but not warranted. Please go to the web to make sure that you have the latest revision.

| DATE            | REVISION | CHANGE                                                                                            |

|-----------------|----------|---------------------------------------------------------------------------------------------------|

| August 12, 2015 | FN7313.9 | Updated Ordering Information table on page 2. Added Revision History and About Intersil sections. |

### **About Intersil**

Intersil Corporation is a leading provider of innovative power management and precision analog solutions. The company's products address some of the largest markets within the industrial and infrastructure, mobile computing and high-end consumer markets.

For the most updated datasheet, application notes, related documentation and related parts, please see the respective product information page found at <a href="https://www.intersil.com">www.intersil.com</a>.

You may report errors or suggestions for improving this datasheet by visiting www.intersil.com/ask.

Reliability reports are also available from our website at <a href="www.intersil.com/support">www.intersil.com/support</a>

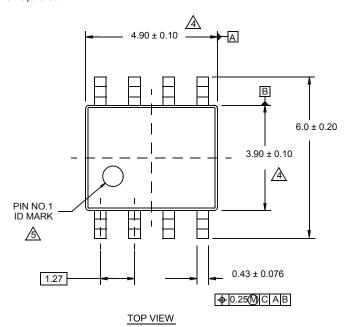

## **Package Outline Drawing**

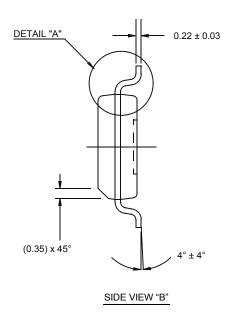

#### M8.15E

## 8 LEAD NARROW BODY SMALL OUTLINE PLASTIC PACKAGE Rev 0, 08/09

#### NOTES:

- Dimensions are in millimeters.

Dimensions in ( ) for Reference Only.

- 2. Dimensioning and tolerancing conform to AMSE Y14.5m-1994.

- 3. Unless otherwise specified, tolerance : Decimal ± 0.05

- Dimension does not include interlead flash or protrusions.

Interlead flash or protrusions shall not exceed 0.25mm per side.

- 5. The pin #1 identifier may be either a mold or mark feature.

- 6. Reference to JEDEC MS-012.

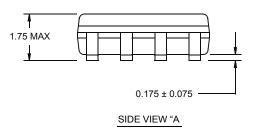

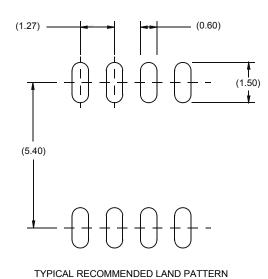

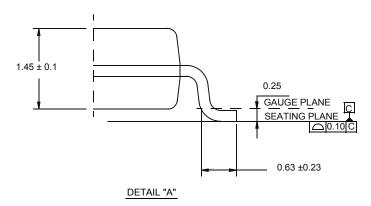

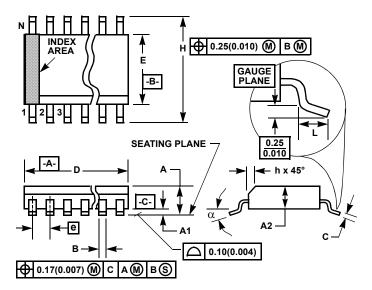

#### Shrink Small Outline Plastic Packages (SSOP) Quarter Size Outline Plastic Packages (QSOP)

#### NOTES:

- Symbols are defined in the "MO Series Symbol List" in Section 2.2 of Publication Number 95.

- 2. Dimensioning and tolerancing per ANSI Y14.5M-1982.

- Dimension "D" does not include mold flash, protrusions or gate burrs.

Mold flash, protrusion and gate burrs shall not exceed 0.15mm (0.006 inch) per side.

- Dimension "E" does not include interlead flash or protrusions. Interlead flash and protrusions shall not exceed 0.25mm (0.010 inch) per side.

- 5. The chamfer on the body is optional. If it is not present, a visual index feature must be located within the crosshatched area.

- 6. "L" is the length of terminal for soldering to a substrate.

- 7. "N" is the number of terminal positions.

- 8. Terminal numbers are shown for reference only.

- Dimension "B" does not include dambar protrusion. Allowable dambar protrusion shall be 0.10mm (0.004 inch) total in excess of "B" dimension at maximum material condition.

- Controlling dimension: INCHES. Converted millimeter dimensions are not necessarily exact.

# M28.15 28 LEAD SHRINK SMALL OUTLINE PLASTIC PACKAGE (0.150" WIDE BODY)

|        | INCHES    |        | MILLI     |       |       |

|--------|-----------|--------|-----------|-------|-------|

| SYMBOL | MIN       | MAX    | MIN       | MAX   | NOTES |

| Α      | 0.053     | 0.069  | 1.35      | 1.75  | -     |

| A1     | 0.004     | 0.010  | 0.10      | 0.25  | -     |

| A2     | -         | 0.061  | -         | 1.54  | -     |

| В      | 0.008     | 0.012  | 0.20      | 0.30  | 9     |

| С      | 0.007     | 0.010  | 0.18      | 0.25  | -     |

| D      | 0.386     | 0.394  | 9.81      | 10.00 | 3     |

| E      | 0.150     | 0.157  | 3.81      | 3.98  | 4     |

| е      | 0.025 BSC |        | 0.635 BSC |       | -     |

| Н      | 0.228     | 0.244  | 5.80      | 6.19  | -     |

| h      | 0.0099    | 0.0196 | 0.26      | 0.49  | 5     |

| L      | 0.016     | 0.050  | 0.41      | 1.27  | 6     |

| N      | 28        |        | 2         | 28    | 7     |

| α      | 0°        | 8°     | 0°        | 8°    | -     |

Rev. 1 6/04

© Copyright Intersil Americas LLC 2003-2015. All Rights Reserved.

All trademarks and registered trademarks are the property of their respective owners.

For additional products, see <a href="https://www.intersil.com/en/products.html">www.intersil.com/en/products.html</a>

Intersil products are manufactured, assembled and tested utilizing ISO9001 quality systems as noted in the quality certifications found at <a href="https://www.intersil.com/en/support/qualandreliability.html">www.intersil.com/en/support/qualandreliability.html</a>

Intersil products are sold by description only. Intersil may modify the circuit design and/or specifications of products at any time without notice, provided that such modification does not, in Intersil's sole judgment, affect the form, fit or function of the product. Accordingly, the reader is cautioned to verify that datasheets are current before placing orders. Information furnished by Intersil is believed to be accurate and reliable. However, no responsibility is assumed by Intersil or its subsidiaries for its use; nor for any infringements of patents or other rights of third parties which may result from its use. No license is granted by implication or otherwise under any patent or patent rights of Intersil or its subsidiaries.

For information regarding Intersil Corporation and its products, see <a href="https://www.intersil.com">www.intersil.com</a>

## **Mouser Electronics**

**Authorized Distributor**

Click to View Pricing, Inventory, Delivery & Lifecycle Information:

Renesas Electronics:

EL5174ISZ EL5174ISZ-T13 EL5174ISZ-T7