## AR1025 FM Radio

Stereo Short Antenna FM Radio Receiver

**Preliminary Datasheet**

VERSION 0.20 23-Aug-2011

Airoha Technology Corp.

This document is commercially confidential and must NOT be disclosed to third parties without prior consent. The information provided herein is believed to be reliable. But production testing may not include testing of all parameters. AIROHA Technology Corp. reserves the right to change information at any time without notification. (<a href="https://www.airoha.com.tw">https://www.airoha.com.tw</a> TEL:+886-3-6128800 FAX:+886-3-6128833 sales@airoha.com.tw)

This document is commercially confidential and must **NOT** be disclosed to third parties without prior consent.

The information provided herein is believed to be reliable. But production testing may not include testing of all parameters. AIROHA Technology Corp. reserves the right to change information at any time without notification.

## **Revision History**

| Version | Change Summary   | Date        | Author   |

|---------|------------------|-------------|----------|

| 0.10    | Created          | 27-Jul-2011 | Raindrop |

| 0.20    | Schematic update | 23-Aug-2011 | Raindrop |

|         |                  |             |          |

|         |                  |             |          |

|         |                  |             |          |

## **INDEX**

| R | evisi | on History                             | 3  |

|---|-------|----------------------------------------|----|

| 1 |       | eatures                                |    |

| 2 | D     | Description                            | 5  |

| 3 | Р     | in Assignment                          | 6  |

|   | 3.1   | Pin Name Description                   | 7  |

| 4 |       | llock Diagram and Description          |    |

|   |       | General Description                    |    |

|   | 4.2   | Radio Receiver                         | 8  |

|   | 4.3   | FM signal processing Unit              | 9  |

|   | 4.4   | Serial 2-Wire Interface                | 9  |

| 5 |       | lectrical Characteristics              |    |

|   | 5.1   | Absolute Maximum Ratings               | 11 |

|   | 5.2   | DC Electrical Specifications           | 11 |

|   | 5.3   | AC Electrical Specification            | 12 |

| 6 | P     | ackage Dimension                       | 13 |

| 7 | S     | chematic                               | 15 |

|   | 7.1   | Crystal solution                       | 15 |

|   | 7.2   | External Clock solution ( 32.768 KHz ) | 16 |

|   | 7.3   | External Clock solution ( 24 MHz )     | 17 |

### 1 Features

- Support short antenna

- Worldwide FM band support: 64MHz~108MHz

- Highest integration level with minimized external BOM cost

- Frequency synthesizer with integrated VCO and Automatic Frequency Control (AFC)

- Integrated XO with external reference clock input (32.768KHz, 32KHz, 4.5MHz, 12MHz, 13MHz, 19.2MHz, 24MHz, 26Mhz, 27MHz, 38.4MHz) or external 32.768KHz crystal

- Automatic Gain Control (AGC) on LNA/VGA amplifiers

- Signal strength measurement

- Programmable de-emphasis time constant (50/75us)

- Adaptive noise suppression

- Analog output with volume control and Line-level outputs

- Serial control interface for 2-wire mode

- Embedded Seek tuning function

- Integrated LDO regulators support 2.2V to 3.6 V supply voltage

- Support  $32\Omega$  resistance loading

- MSOP 3x4.9x1mm 10-pin package

## 2 Description

AR1025 is a highly integrated single chip stereo FM radio receiver. Based on Airoha's advanced and mature FM technology, AR1025 inherits all the legacy features of Airoha's FM product line like supporting worldwide FM bands from 64MHz to 108MHz, integrating LNA, Mixer, Oscillator and LDO to minimize the external BOM cost, and built-in FM signal processing unit with noise reduction mechanism to provide optimum sound quality.

Moreover, knowing FM designers want to throw away lengthy earphone antenna, AR1025 supports short antenna without sacrificing receiving quality. This makes the designers easily develop compact and high quality FM solution.

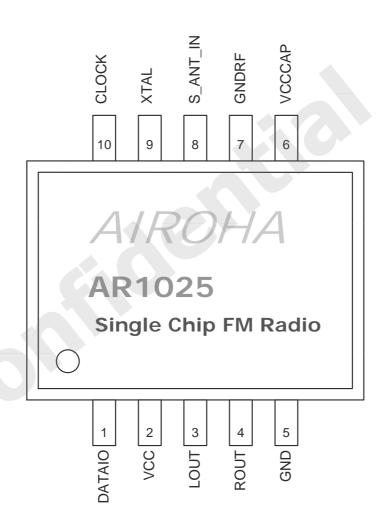

# 3 Pin Assignment

## 3.1 Pin Name Description

| PIN | SIGANL   | TYPE                   | DESCRIPTION                      |  |

|-----|----------|------------------------|----------------------------------|--|

| 1   | DATAIO   | Input/Output, Digital  | Serial Interface                 |  |

| 2   | VCC      | VCC Supply             | Supply Voltage                   |  |

| 3   | LOUT     | Output, Analog         | Left Audio Output                |  |

| 4   | ROUT     | Output, Analog         | Right Audio Output               |  |

| 5   | GND      | GND                    | Ground                           |  |

| 6   | VCCCAP   | Analog                 | VCC Capacitor Pin                |  |

| 7   | GNDRF    | GND                    | RF Ground                        |  |

| 8   | S_ANT_IN | Input, Analog          | Short Antenna Input              |  |

| 9   | XTAL     | Analog                 | XTAL Input/External REFCLK input |  |

| 10  | CLOCK    | Input, Digital Control | Serial Interface                 |  |

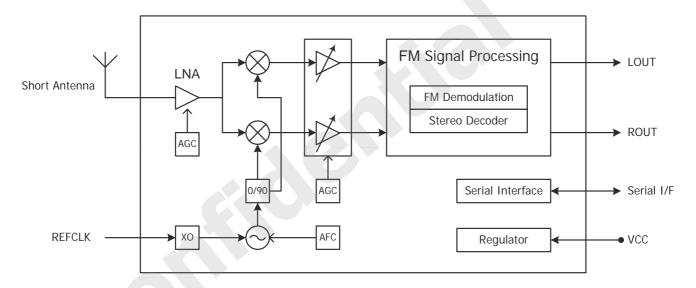

## 4 Block Diagram and Description

### 4.1 General Description

AR1025 is a single chip FM radio receiver IC, which supports full 64MHz to 108MHz band and short antenna. AR1025 integrates on-chip LNA, Mixer, VGA, XO, FM signal processing unit, serial digital I/O interfaces and regulator. The highest integration level minimizes external BOM cost and provides optimum sound quality.

#### 4.2 Radio Receiver

The Radio Receiver part comprises a LNA, a Low-IF mixer and a VGA. The front-end gain of the LNA could be adjusted automatically and thus optimize the received signal-to-noise ratio. The RF signal is then converted to Low-IF band and amplified by the VGA, which is also automatically adjusted. After then the received signal is fed into the FM signal processing unit.

An internal reference oscillator is integrated, so only an external 32.768KHz crystal or a

REFCLK signal is required. (32.768KHz, 32KHz, 4.5MHz, 12MHz, 13MHz, 19.2MHz, 24MHz, 26Mhz, 27MHz, 38.4MHz)

### 4.3 FM signal processing Unit

The main function of the FM signal processing unit includes FM Demodulation and Stereo Decoding . The received FM signal at VGA output is first demodulated into stereo multiplexed signals (Left+Right and Left-Right) and then decoded into Left and Right signals individually by the stereo decoder. Two time constants (50µs or 75µs) of de-emphasis are provided and programmable through the serial interface.

The decoded stereo signals are output to the LOUT and ROUT pins. The output volume could be adjusted or mute through the serial interface. The stereo output could be blocked and only mono signal is output under weak signals.

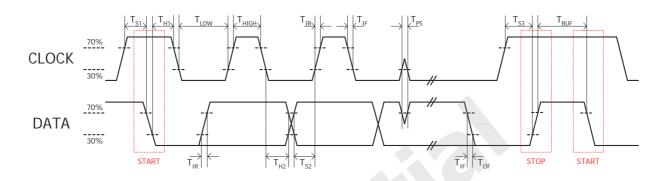

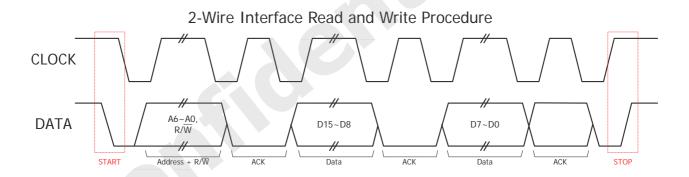

### 4.4 Serial 2-Wire Interface

Serial 2-wire interfaces are provided to read and write the control registers.

| SYMBOL          | PARAMETER                                     |      | TYP | MAX | UNIT |

|-----------------|-----------------------------------------------|------|-----|-----|------|

|                 | CLOCK Frequency                               | 0    |     | 400 | KHz  |

| T <sub>S1</sub> | CLOCK Input to DATA N-edge Setup time (START) | 600  |     |     | ns   |

| T <sub>H1</sub> | CLOCK Input to DATA N-edge Hold time (START)  | 600  |     |     | ns   |

| T <sub>S2</sub> | DATA Input to CLOCK P-edge Setup time         | 100  |     |     | ns   |

| T <sub>H2</sub> | DATA Input to CLOCK N-edge Hold time          | 0    |     | 900 | ns   |

| T <sub>S3</sub> | CLOCK Input to DATA P-edge Setup time (STOP)  | 600  |     |     | ns   |

| $T_BUF$         | STOP to START time                            | 1300 |     |     | ns   |

| $T_{OF}$        | DATA Output Fall time                         | 20   |     | 250 | ns   |

| $T_IR$          | DATA Input & CLOCK Rise time                  | 20   |     | 300 | ns   |

| $T_{IF}$        | DATA Input & CLOCK Fall time                  | 20   |     | 300 | ns   |

| $T_{HIGH}$      | CLOCK HIGH duration                           | 600  |     |     | ns   |

| $T_LOW$         | CLOCK LOW duration                            | 1300 |     |     | ns   |

| $T_{PS}$        | Input Filter Pulse Suppression                |      |     | 50  | ns   |

#### 2-Wire Interface Read and Write Timing Parameters

## **5 Electrical Characteristics**

### 5.1 Absolute Maximum Ratings

AR1025 could be damaged by any stress in excess of the absolute maximum ratings listed below.

| ITEM                       | MIN.   | MAX.               |

|----------------------------|--------|--------------------|

| Power supply voltage (VCC) | - 0.3V | 3.6V               |

| Pin voltage                | - 0.3V | HOST_IO_VCC + 0.3V |

| Maximum power dissipation  |        | 1W                 |

| Operating temperature      | - 40°C | +85°C              |

| Storage temperature        | - 65°C | +150°C             |

| LNA input level            |        | +10 dBm            |

## 5.2 DC Electrical Specifications

Recommended operating ambient temperature range  $T_A = -20$  to  $85^{\circ}C$

| Item                                  | Symbol           | Test Condition                | Min.    | Тур. | Max.    | Unit |

|---------------------------------------|------------------|-------------------------------|---------|------|---------|------|

| VCC Supply Voltage                    | VCC              |                               | 2.2     |      | 3.6     | ٧    |

| VCC Supply Current                    | I <sub>VCC</sub> | ENABLE=1                      |         | 21   |         | mA   |

| Power Down Current                    | I <sub>VCC</sub> | ENABLE=0                      |         | TBD  |         | μA   |

| Digital Input Voltage – High Level    | V <sub>IH</sub>  |                               | 0.7*VCC |      | VCC+0.3 | V    |

| Digital Input Voltage – Low Level     | V <sub>IL</sub>  |                               | - 0.3   |      | 0.3*VCC | V    |

| Digital Input Current – High Level    | I <sub>IH</sub>  | V <sub>IN</sub> =VCC=3.6V     | -10     |      | 10      | μA   |

| Digital Input Current – Low Level     | I <sub>IL</sub>  | V <sub>IN</sub> =0V, VCC=3.6V | -10     |      | 10      | μA   |

| Interface Output Voltage – High Level | V <sub>OH</sub>  | $I_{OUT} = 500\mu A$          | 0.8*VCC |      |         | V    |

| Interface Output Voltage – Low Level  | V <sub>OL</sub>  | I <sub>OUT</sub> = - 500μA    |         |      | 0.2*VCC | V    |

## 5.3 AC Electrical Specification

Typical values are tested under VCC=3.3V, Ta=25°C unless otherwise specified

| PARAMETER                     | CONDITION                   | MIN. | TYP.      | MAX.  | UNIT        |

|-------------------------------|-----------------------------|------|-----------|-------|-------------|

| Input Frequency               |                             | 64   |           | 108   | MHz         |

| Sensitivity                   | (S+N)/N=26dB, FD=22.5KHz    |      | 1.2(-4.5) |       | μVemf(dBuV) |

| LNA Input Resistance          |                             |      | 1.68      |       | ΚΩ          |

| LNA Input Capacitance         |                             |      | 6.87      |       | pF          |

| IIP3                          |                             |      | 86        |       | dΒμV        |

| AM Suppression                | m=0.3                       |      | 70        |       | dB          |

|                               | -200KHz                     |      | 38        |       | dB          |

| Adjacent Channel Selectivity  | +200KHz                     |      | 55        |       | dB          |

| (Low side)                    | -400KHz                     |      | >60       |       | dB          |

|                               | +400KHz                     |      | >60       |       | dB          |

| Spurious Response Rejection   | In-band                     |      | 38        |       | dB          |

| Crystal REFCLK Frequency      |                             |      | 32.768    |       | KHz         |

| External REFCLK Frequency     |                             | 32K  |           | 38.4M | Hz          |

|                               | 25 °C                       | -20  |           | +20   | ppm         |

| REFCLK Frequency Tolerance    | -20 °C ~ +85 °C             | -150 |           | +150  | ppm         |

| Audio Output Voltage *1,      | FD=22.5KHz, at max. vol.    | 85   | 95        | 105   | $mV_{RMS}$  |

| Audio Output L/R Imbalance *1 | FD=75KHz                    | -0.5 |           | 0.5   | dB          |

| Audio Stereo Separation *1    | FD=75KHz including 9% pilot |      | 40        |       | dB          |

| Audio S/N *1                  | FD=22.5KHz                  |      | 56        |       | dB          |

| Audio THD *1,                 | FD=75KHz                    |      | 0.1       |       | %           |

|                               |                             |      | 75        |       | μs          |

| De-emphasis Time Constant     |                             |      | 50        |       | μs          |

| Audio Common-mode Voltage     |                             |      | 0.85      |       | V           |

| Audio Output Load Resistance  | Single-end                  | 32   |           |       | Ω           |

note \*1: VRF=60dBuV

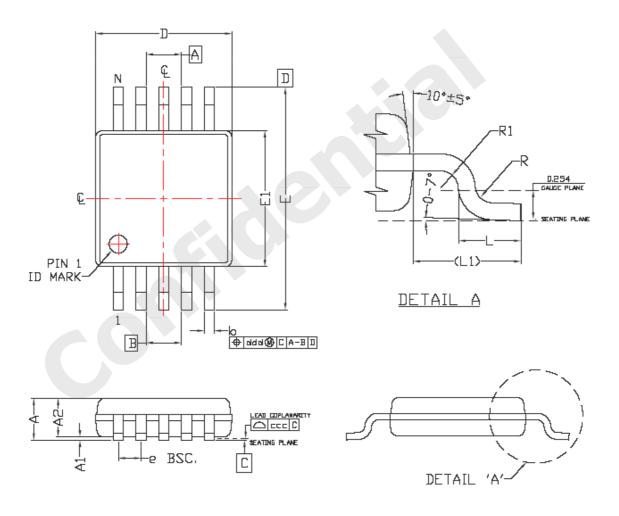

## 6 Package Dimension

Package:MSOP-10pin/3x4.9x1mm/0.5 pitch,

| SYMBOL | 10L MSOP |      |      |  |  |

|--------|----------|------|------|--|--|

| S      | MIN      | N□M. | MAX. |  |  |

| Α      |          |      | 1.10 |  |  |

| A1     | 0.00     |      | 0.15 |  |  |

| A2     | 0.75     | 0.85 | 0.95 |  |  |

| b      | 0.17     | 0.33 |      |  |  |

| D      | 2.90     | 3.10 |      |  |  |

| E      | 4.70     | 5.10 |      |  |  |

| E1     | 2.90     | 3.10 |      |  |  |

| R      | 0.07     |      |      |  |  |

| R1     | 0.07     |      |      |  |  |

| L      | 0.40     | 0.55 | 0.70 |  |  |

| L1     | 0.95 REF |      |      |  |  |

| е      | 0.50 BSC |      |      |  |  |

| ddd    | 0.08     |      |      |  |  |

| CCC    | 0.10     |      |      |  |  |

| N      | 10       |      |      |  |  |

#### Notes

- 1. ALL DIMENSIONS ARE IN MILLIMETERS (ANGLES IN DEGREES).

2. DIMENSIONING AND TOLERANCING PER ANSI Y14.5M-1994.

3. DIMENSION 'D' DOES NOT INCLUDE MOLD FLASH ,PROTRUSIONS OR GATE BURRS.

4. DIMENSION 'E1' DOES NOT INCLUDE INTERNAL FLASH OR PROTRUSION.

5. DIMENSION 'b' DOES NOT INCLUDE DAMBAR PROTRUSION.

6. FOOT LENGTH "L" IS MEASURED AT GAGE PLANE,AT 0.254 ABOVE THE SEATING PLANE.

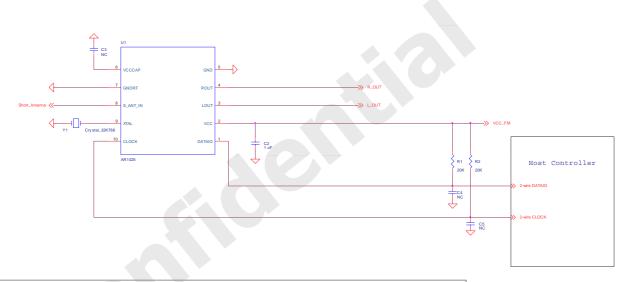

## 7 Schematic

## 7.1 Crystal solution

```

Notel: The pull-high resistors (R2&R1) must be added on 2-wire CLOCK(pinl0) & DATAIO(pinl) respectively.

20K ohm resistors are recommended.

Note2: C4 and C5 must be reserved for fine tune performance.

The two capacitors should be close to Host Controller.

Note3: C2(luF) must be as close to VCC(pin2) as possible.

Note4: C3 must be reserved on PCB and it should be close to pin6.

Note5: Y1 should be as close to pin9 as possible.

```

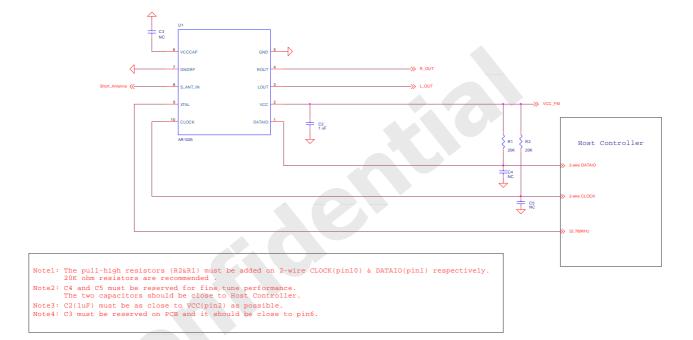

## 7.2 External Clock solution (32.768 KHz)

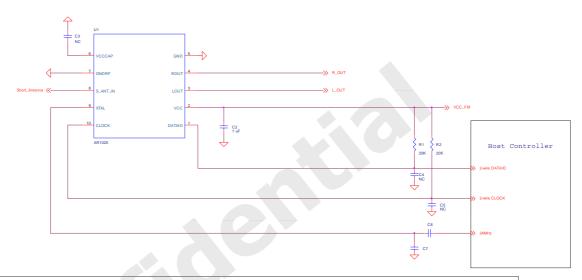

## 7.3 External Clock solution (24 MHz)

```

Note1: The pull-high resistors (R2&R1) must be added on 2-wire CLOCK(pin10) & DATAIO(pin1) respectively.

20K ohm resistors are recommended.

Note2: C4 and C5 must be reserved for fine tune performance.

The two capacitors should be close to Host Controller.

Note3: C2(1uF) must be as close to VCC(pin2) as possible.

Note4: C3 must be reserved on PCB and it should be close to pin6.

Note5: The external clock swing to AR1025 pin9 should be 0.9-0.8Vpp(C6 and C7 shouled be fine tuned) for the best performance.

C6 and C7 should be close to Host Controller, too.

```