### MC75365

### Specifications and Applications Information

# QUAD MOS CLOCK DRIVER OR HIGH-VOLTAGE, HIGH-CURRENT NAND DRIVER

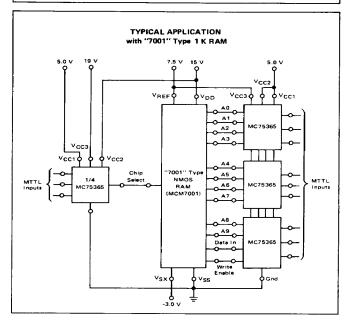

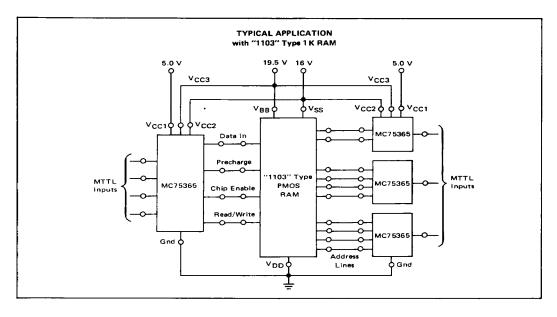

The MC75365 is intended for driving the highly capacitive Address, Control and Timing inputs on a variety of MOS RAMs such as the "1103" and "7001" types. It is designed to operate from the MTTL 5.0 V power supply and the VSS and VBB power supplies used with the memories in most applications. Operation is recommended at VCC3  $\simeq$  VCC2 + 3 V, but the part is useable over a wide latitude of supply voltages. VCC2 may be tied directly to VCC3 in many conditions.

- Pin Compatible with Intel 3207 and Interchangeable with T. I. SN75365

- MTTL and MDTL Compatible, Diode-Clamped Inputs

- Two Common Enable Inputs per Gate Pair

- Low Standby Power Consumption Transient

- Capable of Driving High Capacitive Loads

- Fast Switching Operation

#### QUAD MOS CLOCK DRIVER

SILICON MONOLITHIC INTEGRATED CIRCUITS

### MAXIMUM RATINGS (T<sub>A</sub> = 25°C unless otherwise noted)

| Rating                                  | Symbol              | Value       | Unit               |  |

|-----------------------------------------|---------------------|-------------|--------------------|--|

| Power Supply Voltages                   | V <sub>CC1</sub>    | -0.5 to 7.0 | V                  |  |

|                                         | V <sub>CC2</sub>    | -0.5 to 25  |                    |  |

|                                         | V <sub>CC3</sub>    | -0.5 to 30  |                    |  |

| Input Voltage                           | V <sub>I</sub>      | 5.5         | V                  |  |

| Input Differential Voltage (see Note 1) | V <sub>ID</sub>     | 5.5         | V                  |  |

| Power Dissipation (Package Limitation)  |                     |             |                    |  |

| Ceramic Package @ T <sub>A</sub> = 25°C | PD                  | 1000        | mW                 |  |

| Derate above T <sub>A</sub> = 25°C      | 1/R <sub>0JA</sub>  | 6.6         | mW/ <sup>O</sup> C |  |

| Plastic Package @ TA = 25°C             | PD                  | 830         | mW                 |  |

| Derate above TA = 25°C                  | 1/R <sub>0</sub> JA | 6.6         | mW/°C              |  |

| Ceramic Package @ T <sub>C</sub> = 25°C | PD                  | 3.0         | Watts              |  |

| Derate above $T_C = 25^{\circ}C$        | 1/R <sub>0</sub> JC | 20          | mW/ <sup>O</sup> C |  |

| Plastic Package @ T <sub>C</sub> = 25°C | PD                  | 1.8         | Watts              |  |

| Derate above T <sub>C</sub> = 25°C      | 1/R <sub>0</sub> JC | 14          | mW/ <sup>o</sup> C |  |

| Operating Ambient Temperature Range     | TA                  | 0 to 70     | °C                 |  |

| Junction Temperature                    | Тј                  | 1           | °C                 |  |

| Ceramic Package                         |                     | 175         |                    |  |

| Plastic Package                         |                     | 150         |                    |  |

| Storage Temperature Range               | T <sub>stg</sub>    | -65 to +150 | οс                 |  |

Note 1. This is the differential voltage between any two inputs to any single gate.

#### RECOMMENDED OPERATING CONDITIONS

| Characteristic                                           | Symbol                             | Min              | Тур | Max  | Unit |

|----------------------------------------------------------|------------------------------------|------------------|-----|------|------|

| Power Supply Voltages                                    | V <sub>CC1</sub>                   | 4.75             | 5.0 | 5.25 | T ~  |

|                                                          | V <sub>CC2</sub>                   | 4.75             | 20  | 24   |      |

|                                                          | V <sub>CC3</sub>                   | V <sub>CC2</sub> | 24  | 28   |      |

| Difference between V <sub>CC3</sub> and V <sub>CC2</sub> | V <sub>CC3</sub> -V <sub>CC2</sub> | 0                | 4.0 | 10   | V    |

| Operating Temperature Range                              | TA                                 | 0                | -   | 70   | °C   |

ELECTRICAL CHARACTERISTICS (Unless otherwise noted  $T_A$  = 25°C,  $V_{CC1}$  = 5.0 V,  $V_{CC2}$  = 20 V,  $V_{CC3}$  = 24 V,  $C_L$  = 200 pF,  $R_D$  = 24 $\Omega$ , See Figures 1 and 2.)

| Characteristic                                                                                                                                                                                                                                                                                                                 | Symbol                                                                                                          | Min                                                                                              | Typ*                                                                                             | Max                                     | Unit |

|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----------------------------------------------------------------------------------------------------------------|--------------------------------------------------------------------------------------------------|--------------------------------------------------------------------------------------------------|-----------------------------------------|------|

| Input Voltage - High Logic State                                                                                                                                                                                                                                                                                               | VIH                                                                                                             | 2.0                                                                                              | _                                                                                                | _ 1                                     | v    |

| Input Voltage – Low Logic State                                                                                                                                                                                                                                                                                                | VIL                                                                                                             | -                                                                                                |                                                                                                  | 0.8                                     |      |

| Input Clamp Voltage {I <sub>IC</sub> = -12 mA}                                                                                                                                                                                                                                                                                 | VIC                                                                                                             | -                                                                                                | _                                                                                                | 1.5                                     | V    |

| Input Current — Maximum Input Voltage<br>(VIH = 5.5 V)                                                                                                                                                                                                                                                                         | UH1                                                                                                             |                                                                                                  | _                                                                                                | 1.0                                     | mA   |

| Input Current — High Logic State<br>(V <sub>IH</sub> (1) = 2.4 V)<br>(V <sub>IH</sub> (2) or V <sub>IH</sub> (3) = 2.4 V)                                                                                                                                                                                                      | IIH2                                                                                                            |                                                                                                  | <del>-</del>                                                                                     | 40<br>80                                | μΑ   |

| Input Current — Low Logic State<br>(V <sub>IL</sub> (1) = 0.4 V)<br>(V <sub>IL</sub> (2) or V <sub>IL</sub> (3) = 0.4 V)                                                                                                                                                                                                       | IIL                                                                                                             |                                                                                                  | -1.0<br>-2.0                                                                                     | -1.6<br>-3.2                            | mA   |

| Output Voltage — High Logic State  (VCC3 = VCC2 + 3.0 V, V <sub>I</sub> L = 0.8 V, I <sub>OH</sub> = -100 µA)  (VCC3 = VCC2 + 3.0 V, V <sub>I</sub> L = 0.8 V, I <sub>OH</sub> = -10 mA)  (VCC3 = VCC2, V <sub>I</sub> L = 0.8 V, I <sub>OH</sub> = -50 µA)  (VCC3 = VCC2, V <sub>I</sub> L = 0.8 V, I <sub>OH</sub> = -10 mA) | V <sub>OH1</sub><br>V <sub>OH2</sub><br>V <sub>OH3</sub><br>V <sub>OH4</sub>                                    | V <sub>CC2</sub> -0.3<br>V <sub>CC2</sub> -1.2<br>V <sub>CC2</sub> -1.0<br>V <sub>CC2</sub> -2.3 | V <sub>CC2</sub> -0.1<br>V <sub>CC2</sub> -0.9<br>V <sub>CC2</sub> -0.7<br>V <sub>CC2</sub> -1.8 | -<br>-<br>-<br>-                        | V    |

| Output Clamp Voltage<br>(V <sub>IL</sub> = 0 V, I <sub>OC</sub> = 20 mA)                                                                                                                                                                                                                                                       | Voc                                                                                                             | -                                                                                                |                                                                                                  | V <sub>CC2</sub> +1.5                   | V    |

| Output Voltage – Low Logic State $(V_{IH} = 2.0 \text{ V, } I_{OL} = 10 \text{ mA})$ $\{15 \text{ V} \le V_{CC3} \le 28 \text{ V, } V_{IH} = 2.0 \text{ V, } I_{OL} = 40 \text{ mA}\}$                                                                                                                                         | VOL1<br>VOL2                                                                                                    | _                                                                                                | 0.15<br>0.25                                                                                     | 0.3<br>0.5                              | ٧    |

| Power Supply Currents — Outputs High Logic State  (VCC1 = 5.25 V, VCC2 = 24 V, VCC3 = 28 V,  VIL = 0 V, I <sub>OH</sub> = 0 mA)  (VCC1 = 5.25 V, VCC2 = 24 V, VCC3 = 24 V  VIL = 0 V, I <sub>OH</sub> = 0 mA)                                                                                                                  | <sup>1</sup> СС1(H)<br><sup>1</sup> СС2(H)<br><sup>1</sup> СС3(H)<br><sup>1</sup> СС2(H)<br><sup>1</sup> СС3(H) | -<br>-<br>-<br>-                                                                                 | 4.0<br>-2.2<br>2.2<br>-                                                                          | 8.0<br>-3.2/+0.25<br>3.5<br>0.25<br>0.5 | mA   |

| Power Supply Currents — Output Low Logic State<br>(VCC1 = 5.25 V, VCC2 = 24 V, VCC3 = 28 V<br>V <sub>1H</sub> = 5.0 V, I <sub>OL</sub> = 0 mA)                                                                                                                                                                                 | ICC1(L)<br>ICC2(L)<br>ICC3(L)                                                                                   | _<br>_<br>_                                                                                      | 31<br>-<br>16                                                                                    | 47<br>2.5<br>25                         | mA   |

| Power Supply Currents — Standby Condition<br>(VCC1 = 0 V, VCC2 = 24 V, VCC3 = 24 V<br>VIH = 5.0 V, IOL = 0 mA)                                                                                                                                                                                                                 | CC2(S)                                                                                                          | <u>-</u>                                                                                         | -<br>-                                                                                           | 0.25<br>0.5                             | mA   |

<sup>\*</sup>Typical Values at 25°C,  $V_{CC1}$  = 5.0 V,  $V_{CC2}$  = 20 V and  $V_{CC3}$  = 24 V

# SWITCHING CHARACTERISTICS (Unless otherwise noted TA = 25°C, V<sub>CC1</sub> = 5.0 V, V<sub>CC2</sub> = 20 V, V<sub>CC3</sub> = 24 V, C<sub>L</sub> = 200 pF, R<sub>D</sub> = 24 $\Omega$ , See Figures 1 and 2.)

| Characteristic                                   | Symbol           | Min | Тур | Max | Unit |

|--------------------------------------------------|------------------|-----|-----|-----|------|

| Propagation Delay Time, Low to High State Output | tPLH .           | 10  | 31  | 48  | ns   |

| Propagation Delay Time, High to Low State Output | tPHL             | 10  | 30  | 46  |      |

| Delay Time, Low to High State Output             | <sup>†</sup> DLH | _   | 11  | 20  | ns   |

| Delay Time, High to Low State Output             | <sup>t</sup> DHL | _   | 10  | 18  |      |

| Transition Time, Low to High State Output        | tTLH             |     | 20  | 33  | ns   |

| Transition Time, High to Low State Output        | tTHL             | _   | 20  | 33  | 1    |

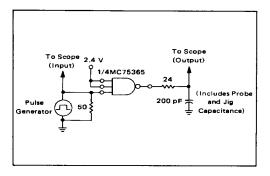

FIGURE 1 - SWITCHING CHARACTERISTIC TEST CIRCUIT

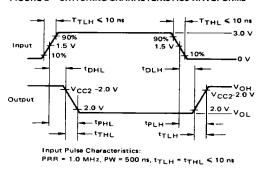

FIGURE 2 - SWITCHING CHARACTERISTICS WAVEFORMS

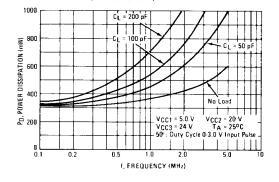

**TYPICAL PERFORMANCE CURVES**

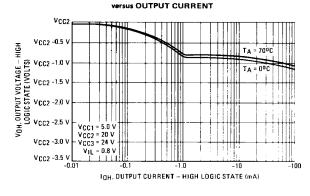

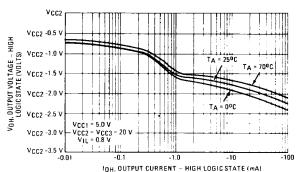

FIGURE 3 – OUTPUT VOLTAGE -- HIGH LOGIC STATE

FIGURE 4 – OUTPUT VOLTAGE – HIGH LOGIC STATE versus OUTPUT CURRENT

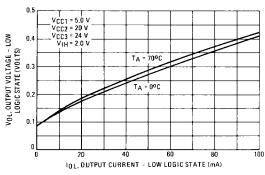

FIGURE 5 – OUTPUT VOLTAGE – LOW LOGIC STATE Versus OUTPUT CURRENT

FIGURE 6 — TOTAL POWER DISSIPATION versus FREQUENCY

(All Four Drivers)

#### **TYPICAL PERFORMANCE CURVES**

#### APPLICATIONS SUGGESTIONS

#### POWER CONSIDERATIONS

Circuit performance and long-term circuit reliability are affected by die temperature. Normally, both are improved by keeping the integrated circuit junction temperatures low. Electrical power dissipated in the integrated circuit is the source of heat. This heat source increases the temperature of the die relative to some reference point, normally the ambient temperature. The temperature increase depends on the amount of power dissipated in the circuit and on the net thermal resistance between the heat source and the reference point. The basic formula for converting power dissipation into junction temperature is:

$$T_{J} = T_{A} + P_{D} (R_{\theta JC} + R_{\theta CA})$$

(1)

or

$$T_{J} = T_{A} + P_{D} (R_{\theta JA})$$

(2)

where

$T_J$  = junction temperature  $T_A$  = ambient temperature  $P_D$  = power dissipation  $R_{\theta JC}$  = thermal resistance, junction to case  $R_{\theta JC}$  = thermal resistance, case to ambient  $R_{\theta JA}$  = thermal resistance, junction to ambient.

Power Dissipation for the MC75365 MOS Clock Driver: The power dissipation of the device (PD) is dependent on the following system requirements: frequency of operation, capacitive loading, output voltage swing, and duty cycle. The variation of power dissipation with frequency and load capacitance for the MC75365 is illustrated in Figure 6. The power dissipation, when substituted into equation (2), should not yield a junction temperature, TJ, greater than TJ(max) at the maximum encountered ambient temperature. TJ(max) is specified for two integrated circuit packages in the maximum ratings section of this data sheet.

With these maximum junction temperature values, the maximum permissible power dissipation at a given ambient temperature may be determined. This can be done with equations (1) and (2) and the maximum thermal resistance values given in Table 1 shown on the following page.

TABLE 1 - THERMAL CHARACTERISTICS OF "L" AND "P" PACKAGES

| PACKAGE TYPE<br>(Mounted in Socket) |     | ( <sup>o</sup> C/W)<br>Il Air | R <sub>OJC</sub> ( <sup>o</sup> C/W)<br>Still Air |     |  |

|-------------------------------------|-----|-------------------------------|---------------------------------------------------|-----|--|

|                                     | MAX | TYP                           | MAX                                               | TYP |  |

| "L" (Ceramic Package)               | 150 | 100                           | 50                                                | 27  |  |

| "P" (Plastic Package)               | 150 | 100                           | 70                                                | 40  |  |

If the power dissipation determined by a given system produces a junction temperature in excess of the recommended maximum rating for a given package type, something must be done to reduce the junction temperature.

There are two methods of lowering the junction temperature without changing the system requirements. First, the ambient temperature may be reduced sufficiently to bring TJ to an acceptable value. Secondly, the R $\theta$ CA term can be reduced. Lowering the R $\theta$ CA term can be accomplished by increasing the surface area of the package with the addition of a heat sink or by blowing air across the package to promote improved heat dissipation.

#### **Heat Sink Considerations:**

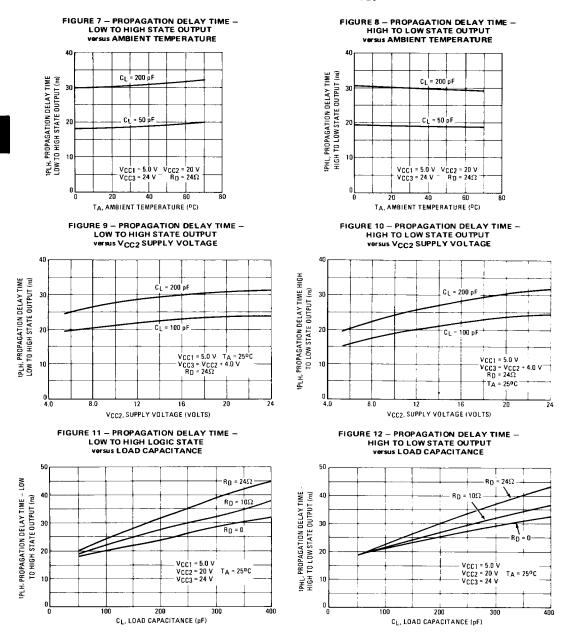

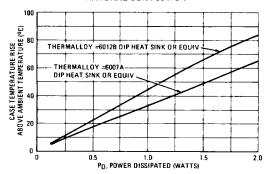

Heat sinks come in a wide variety of sizes and shapes that will accomodate almost any IC package made. Some of these heat sinks are illustrated in Figure 13.

FIGURE 13 - THERMALLOY\* HEAT SINKS

From Table 1,  $R_{\theta}JA(max)$  for the ceramic package with no heat sink and in a still air environment is  $150^{\circ}C/W$ .

For the following example the Thermalloy 6012B type heat sink, or equivalent, is chosen. With this heat sink, the  $R_{\theta CA}$  for natural convection from Figure 14 is 44°C/W. From Table 1  $R_{\theta JC}$ (max) = 50°C/W for the ceramic package. Therefore, the new  $R_{\theta JA}$ (max) with the 6012B heat sink added becomes:

$R_{\theta JA}(max) = 50^{\circ}C/W + 44^{\circ}C/W = 94^{\circ}C/W.$

Thus the addition of the heat sink has reduced  $R_{\theta}JA$  (max) from 150°C/W down to 94°C/W. With the heat sink, the maximum power dissipation by equation (2) at  $T_A$  = +70°C is:

$$P_D = \frac{175^{\circ}C - 70^{\circ}C}{+94^{\circ}C/W} = 1.11 \text{ watts.}$$

This gives approximately a 60% increase in maximum power dissipation over the power dissipation which is allowable with no heat sink.

FIGURE 14 – CASE TEMPERATURE RISE ABOVE

AMBIENT WORSUS POWER DISSIPATED USING

NATURAL CONVECTION

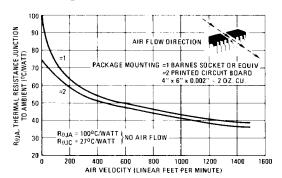

### Forced Air Considerations:

As illustrated in Figure 15, forced air can be employed to reduce the  $R_{\theta JA}$  term. Note, however, that this curve is expressed in terms of typical  $R_{\theta JA}$  rather than maximum  $R_{\theta JA}$ . Maximum  $R_{\theta JA}$  can be determined in the following manner:

From Table 1 the following information is known:

(a)  $R_{\theta JA}(typ) = 100^{\circ}C/W$

(b)  $R_{\theta JC}(typ) = 27^{\circ}C/W$

Since:

$$R_{\theta}JA = R_{\theta}JC + R_{\theta}CA \tag{3}$$

Then:

$$R_{\theta}CA = R_{\theta}JA - R_{\theta}JC \tag{4}$$

Therefore, in still air

$R_{\theta CA}(typ) = 100^{\circ}C/W - 27^{\circ}C/W = 73^{\circ}C/W$

From Curve 1 of Figure 14 at 500 LFPM and equation (4),

$R_{\theta CA}(typ) = 53^{\circ}C/W - 27^{\circ}C/W = 26^{\circ}C/W$ .

Thus R $_{\theta CA}$ (typ) has changed from 73°C/W (still air) to 26°C/W (500 LFPM), which is a decrease in typical R $_{\theta CA}$  by a ratio of 1:2.8. Since the typical value of R $_{\theta CA}$  was reduced by a ratio of 1:2.8, R $_{\theta CA}$ (max) of 100°C/W should also decrease by a ratio of 1:2.8.

This yields an  $R_{\theta CA}$ (max) at 500 LFPM of 36°C/W. Therefore, from equation (3):

$R_{\theta}J_{A}(max) = 50^{\circ}C/W + 36^{\circ}C/W = 86^{\circ}C/W$ . Therefore the maximum allowable power dissipation at 500 LFPM and  $T_{A} = +70^{\circ}C$  is from equation (2):

$$P_D = \frac{175^{\circ}C - 70^{\circ}C}{86^{\circ}C/W} = 1.2 \text{ watts.}$$

## FIGURE 15 — TYPICAL THERMAL RESISTANCE ( $R_{\theta,JA}$ ) OF "L" PACKAGE versus AIR VELOCITY

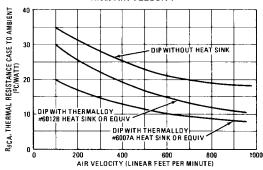

#### Heat Sink and Forced Air Combined:

Some heat sink manufacturers provide data and curves of  $R\theta_{CA}$  for still air and forced air such as illustrated in Figure 16. For example the 6012B heat sink has an  $R\theta_{CA} = 17^{O}\text{C/W}$  at 500 LFPM as noted in Figure 15. From equation (3):

Max R $_{\theta JA} = 50^{\circ}$ C/W + 17°C/W = 67°C/W From equation (2) at T $_{A} = +70^{\circ}$ C

$$P_D = \frac{175^{o}C - 70^{o}C}{67^{o}C/W}$$

1.57 watts.

### FIGURE 16 – THERMAL RESISTANCE $R_{\theta CA}$ versus AIR VELOCITY

Note from Table 1 and Figure 15 that if the 16-pin ceramic package is mounted directly to the PC board (2 oz. cu. underneath), that typical  $R_{\theta,JA}$  is considerably less than for socket mount with still air and no heat sink. The following procedure can be employed to determine the maximum power dissipation for this condition.

Given data from Table 1:

typical  $R_{\theta JA} = 100^{\circ} C/W$ typical  $R_{\theta JC} = 27^{\circ} C/W$

From Curve 2 of Figure 15,  $R_{\theta JA}(typ)$  is  $75^{\circ}C/W$  for a PC mount and no air flow. Then the typical  $R_{\theta CA}$  is  $75^{\circ}C/W - 27^{\circ}C/W = 48^{\circ}C/W$ . From Table 1 the typical value of  $R_{\theta CA}$  for socket mount is  $100^{\circ}C/W - 27^{\circ}C/W = 73^{\circ}C/W$ . This shows that the PC board mount results in a decrease in typical  $R_{\theta CA}$  by a ratio of 1:1.5 below the typical value of  $R_{\theta CA}$  in a socket mount. Therefore, the maximum value of socket mount  $R_{\theta CA}$  of  $100^{\circ}C/W$  should also decrease by a ratio of 1:1.5 when the device is mounted in a PC board. The maximum  $R_{\theta CA}$  becomes:

$$R_{\theta}CA = \frac{100^{\circ}C/W}{1.5} \approx 66^{\circ}C/W$$

for PC board mount

Therefore the maximum R $\theta$ JA for a PC mount is from equation (3).

$R_{\theta,JA} = 50^{\circ}C/W + 66^{\circ}C/W = 116^{\circ}C/W$ .

With maximum  $R_{\theta JA}$  known, the maximum power dissipation can be found. If  $T_A = 70^{\circ}C$  then from equation (2) the maximum power dissipation may be found to be 905 mW.

In most cases, heat sink manufacturer's publish only RACA socket mount data. Although data for PC mounting is generally not available, this should present no problem. Note in Figure 15 that an air flow greater than 250 LFPM yields a socket mount Raja approximately 6% greater than for a PC mount. Therefore, the socket mount data can be used for a PC mount with a slightly greater safety factor. Also it should be noted that thermal resistance measurements can vary widely. These measurement variations are due to the dependency of RhetaCA of the type environment and measurement techniques employed. For example, R<sub>BCA</sub> would be greater for an integrated circuit mounted on a PC board with little or no ground plane versus one with a substantial ground plane. Therefore, if the maximum calculated junction temperature is on the border line of being too high for a given system application, then thermal resistance measurements should be done on the system to be absolutely certain that the maximum junction temperature is not exceeded.