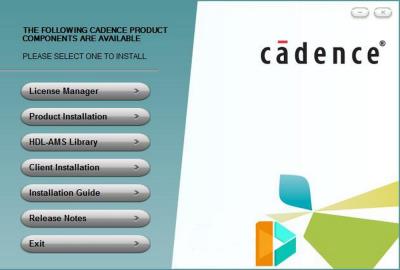

✨ معرفی Cadence Allegro Sigrity 16.62 (x64)

Cadence Allegro Sigrity ابزاری قدرتمند برای تحلیل ارتباطات سیگنال و یکپارچگی توان (Signal & Power Integrity – SI/PI) در طراحی بردهای PCB و بستهبندیهای IC است. نسخه ۱۶٫۶۲ یکی از بهروزترین نسخههاست که قابلیتهای پیشرفتهای برای مهندسین فراهم میآورد.

🌟 ویژگیها (Features)

در این نسخه، امکانات زیر قابل توجهند:

| قابلیت |

توضیح |

| PI Base (PA5800) |

ابزار پایه تحلیل یکپارچگی توان – امکان بررسی DC و تحلیل پایه توان در طرحها؛ ابزار کمکی برای طراحان در فاز طراحی اولیه. |

| Power Feasibility Editor (PFE) |

امکان انتخاب و جایگذاری خازنهای دِکاپلینگ (de-caps) و ایجاد استراتژی مناسب توان برای دستگاه، و تبدیل آن به Constraint Set برای کنترل طراحی. |

| Signoff & Optimization Option (SIGR925) |

تحلیل دقیق برای Sign-off؛ شامل ابزارهایی مثل PowerDC, OptimizePI, PowerSI, و ابزار 3D-EM برای بررسی جامع توان/سیگنال. |

| IO-SSO Analysis Suite (SIGR950) |

تحلیل نویز همزمان کلیدزنی (Simultaneous Switching Noise) در باسهای موازی؛ شبیهسازی و مدلسازی دقیق برای پروتکلهای حافظه مثل DDR3/DDR4؛ بررسی تطابق با مشخصات الکتریکی استاندارد. |

| پشتیبانی از فرمتها و ادغام با محیط طراحی Allegro / SPB |

محیط طراحی Allegro PCB/SPB ترکیب شده با Sigrity؛ امکان تحلیل داخل طراحی (in-design) و بعد از طراحی (post-layout) با مدلهای واقعی. |

| استخراج و مدلسازی پارازیتی / پارامترهای شبکه (S, Z, Y) |

امکان استخراج دادههایی که برای شبیهسازیهای توان/سیگنال ضروریاند؛ بررسی coupling خطوط، امپدانس، انعکاس، Crosstalk، IR drop و غیره. |

| شبیهسازی “What-If” و تحلیل پیش از مسیرگذاری |

به طراحان امکان میدهد سناریوهای مختلف را پیش از اینکه مسیرگذاری نهایی شود آزمایش کنند؛ تحلیل سریع برای تصمیمگیری بهتر. |

⚡ تست پتانسیل (Potential Test)

✅ نقاط قوت

-

دقت بالاتر در تحلیل

ابزارهایی مثل 3D extraction، تحلیل EMI/EMC، SI/PI دقیق باعث میشوند خطاها و مشکلات الکتریکی در برد قبل از تولید شناسایی شوند.

-

کاهش تعداد نسخههای آزمایشی (Prototypes) و بازطراحی (Re-spins)

با تحلیلهای پیشطراحی (pre-layout) و “what if” میتوان مشکلات احتمالی را قبل از مراحل بعدی دید، که هزینه و زمان را کاهش میدهد.

-

بهبود کیفیت محصول و افزایش قابل اطمینان بودن

توان، نویز، امپدانس و مشکلات سیگنال با دقت بیشتری کنترل میشوند.

-

ادغام نزدیک با محیط طراحی

وجود ارتباط مستقیم با Allegro/SPB باعث میشود انتقال داده و تحلیل سریعتر و کم خطاتر انجام گیرد؛ رابط طراحی و آنالیز کمتر جداست.

📋 لیست مکان قطعات (Pick & Place / Placement List)

اطلاعات اصلی که در فایل وجود دارد:

-

Reference Designator (RefDes): شماره شناسایی قطعه (مثل R1, C10, U5)

-

Part Number: کد قطعه یا شماره سفارش

-

Value: مقدار یا مشخصه قطعه (مثلاً 10kΩ, 100nF, ATmega328)

-

Package / Footprint: نوع پکیج یا جایگاه فیزیکی (SOIC-8, 0603, BGA256 و …)

-

X و Y Coordinates: مختصات دقیق قطعه روی برد (بر حسب میلیمتر یا mil)

-

Rotation: زاویه چرخش قطعه روی برد (0°, 90°, 180°, 270°)

-

Side: روی کدام سمت برد نصب شده (Top / Bottom)